Vivado安装使用

vivado操作组合电路

以四选一为例

新建工程

点击Create Project

命名文件,设置路径

不要有中文和空格

选择RTL Project

并且勾选Do not specify sources at this time

目的是为了跳过在新建工程的过程中跳过添加设计源文件,

具体的源文件在创建过程之后添加

需要选择我们设计实验的开发板的型号

选择系列:Artix-7

封装技术:csg324

选择速度等级:-1

选择型号:xc7a35tcsg324-1

确认相关信息是否一致

不一致:点击Back,返回修改

一致则:点击Finish,完成创建

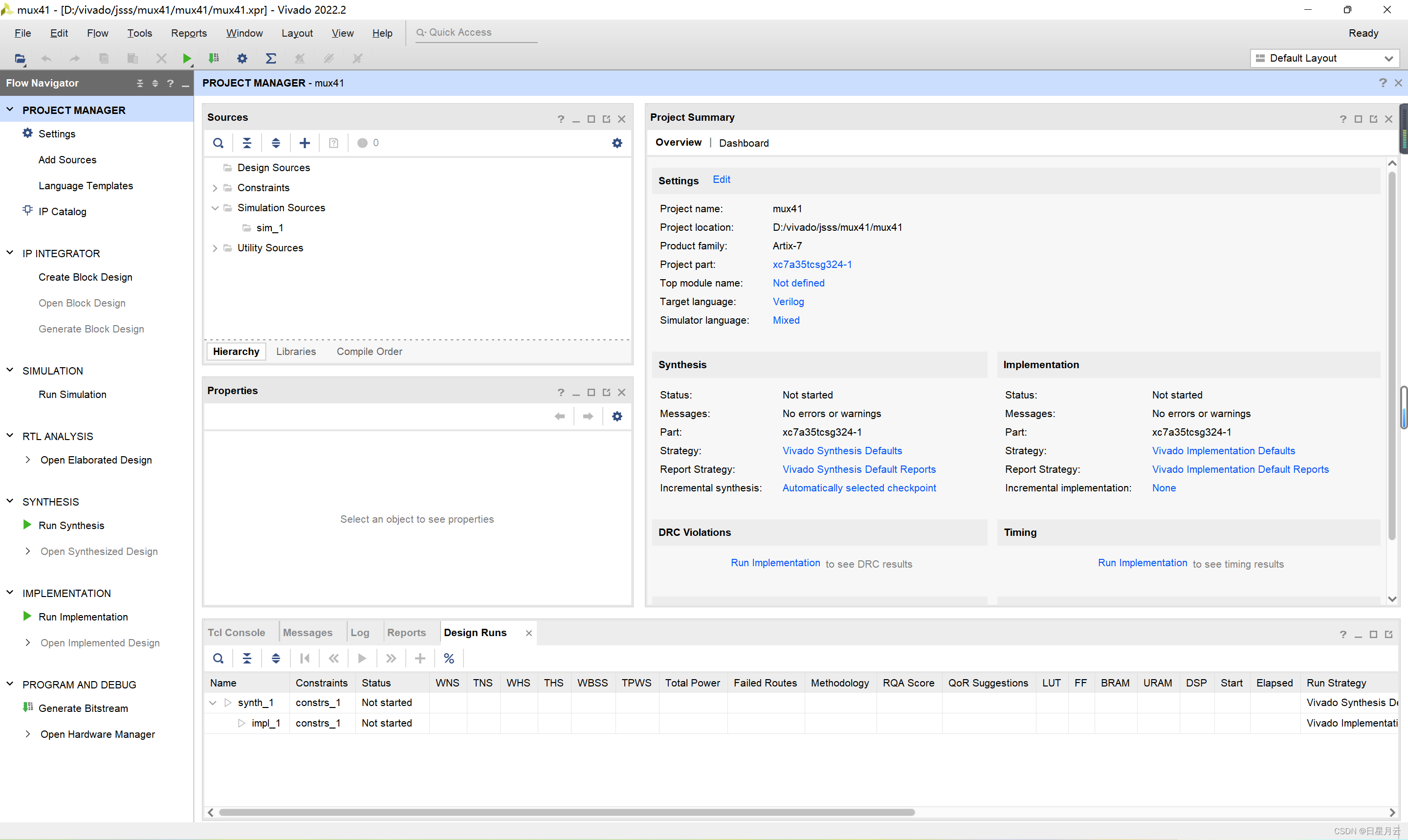

显示如下:

添加源文件

添加源文件

左边导航栏:Add Sources

或者

Source窗口:空白处右键-Add Sources…

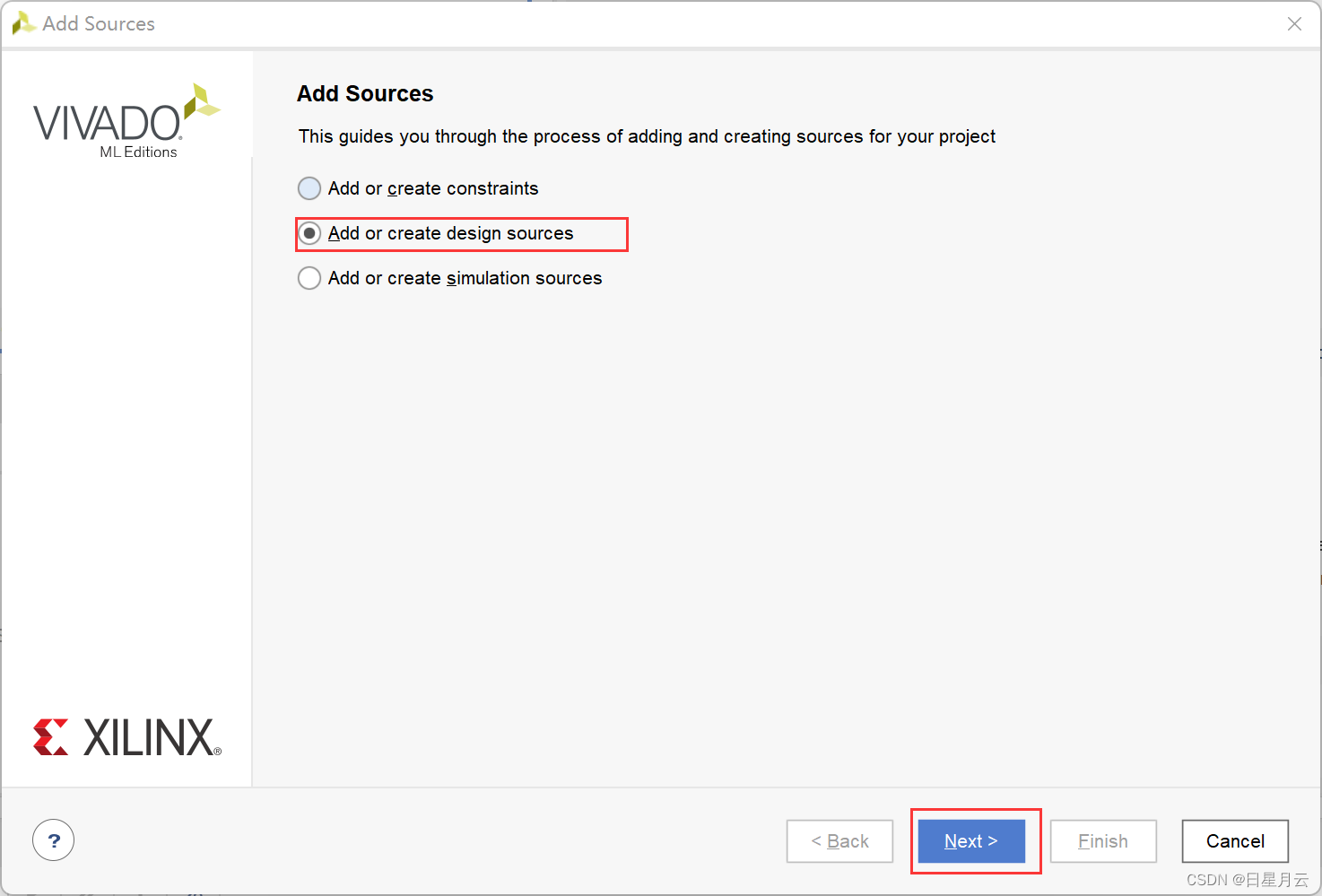

选择第二项:Add or create design sources

给工程添加一个设计文件

选择Add Files:存在设计好的电路.v文件

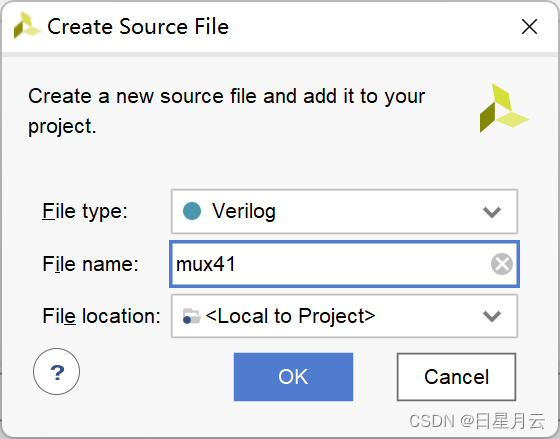

选择Create Files:新建文件

起名字:mux41

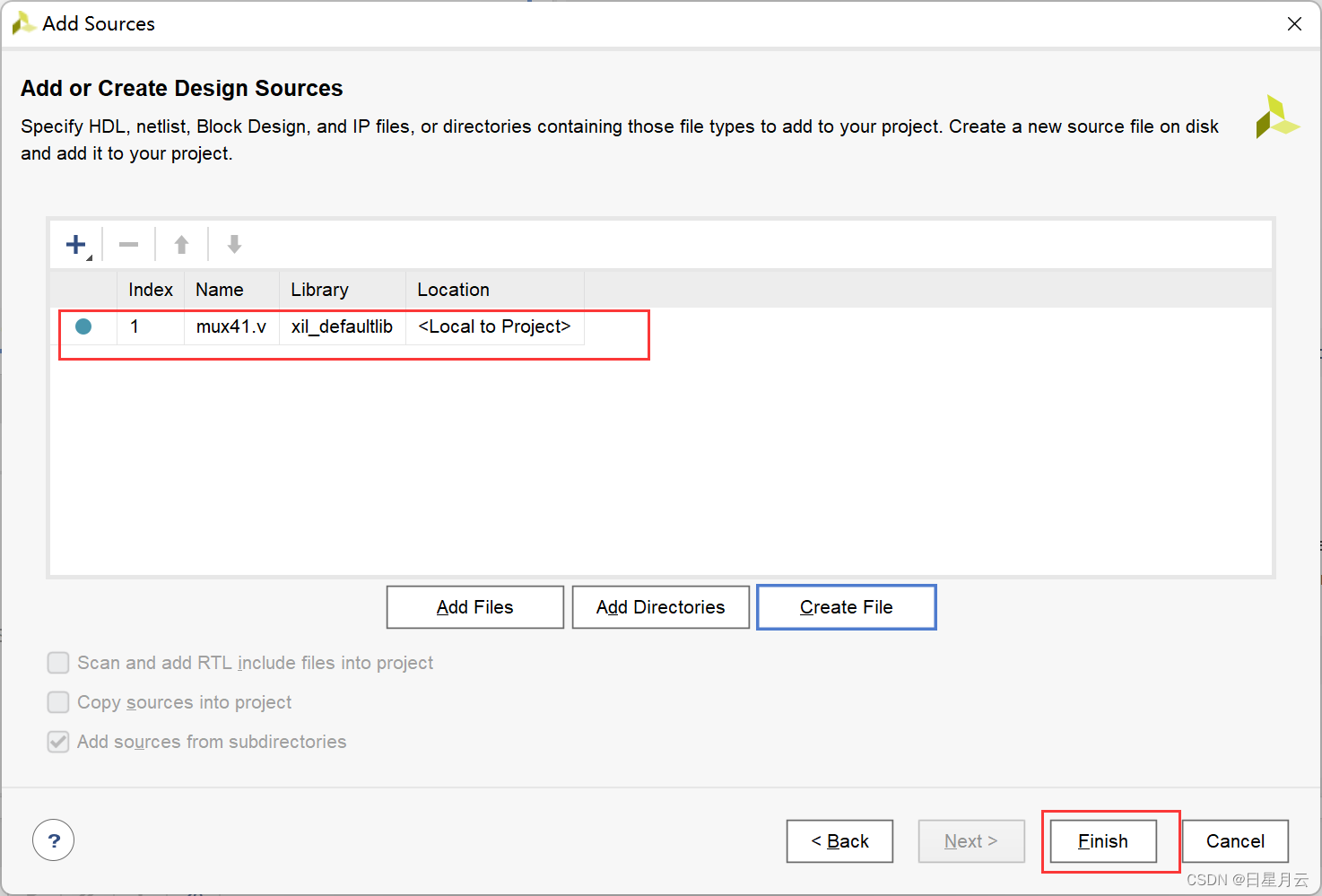

显示如下:单击Finish按钮

可以设置所有端口信号

此处我们在后面设置

单击Yes

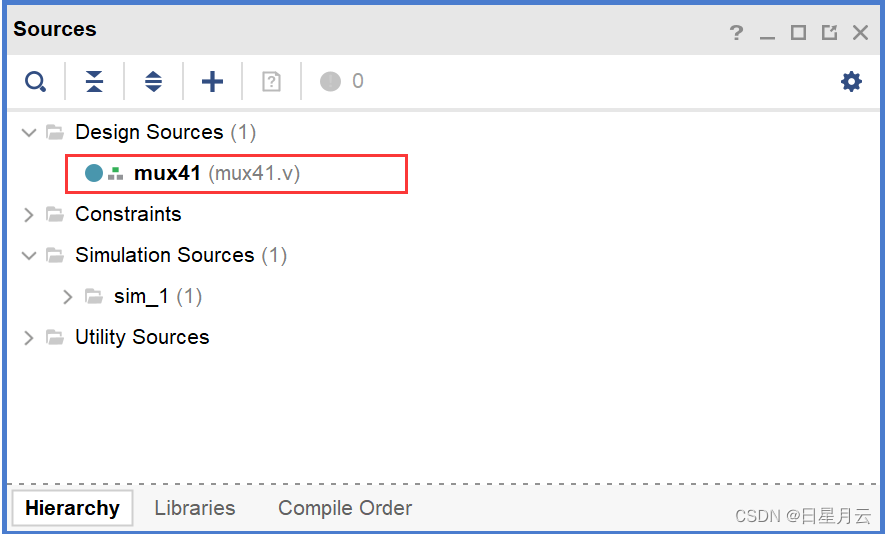

可见:工程中多了mux41.v文件

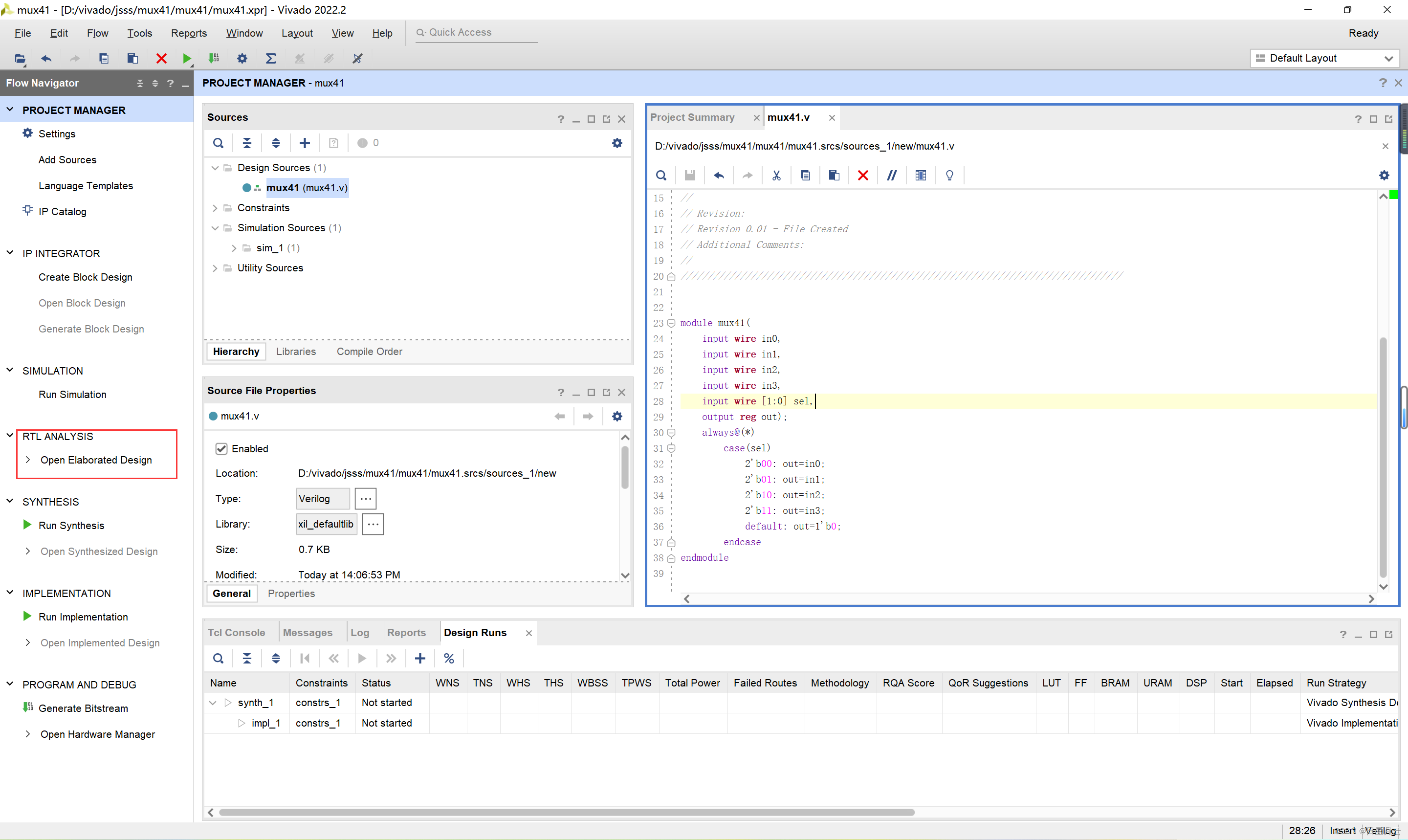

双击打开,可以在右边可以看见

mux41代码

module mux41(

input wire in0,

input wire in1,

input wire in2,

input wire in3,

input wire [1:0] sel,

output reg out);

always@(*)

case(sel)

2'b00: out=in0;

2'b01: out=in1;

2'b10: out=in2;

2'b11: out=in3;

default: out=1'b0;

endcase

endmodule

保存 Ctrl+S

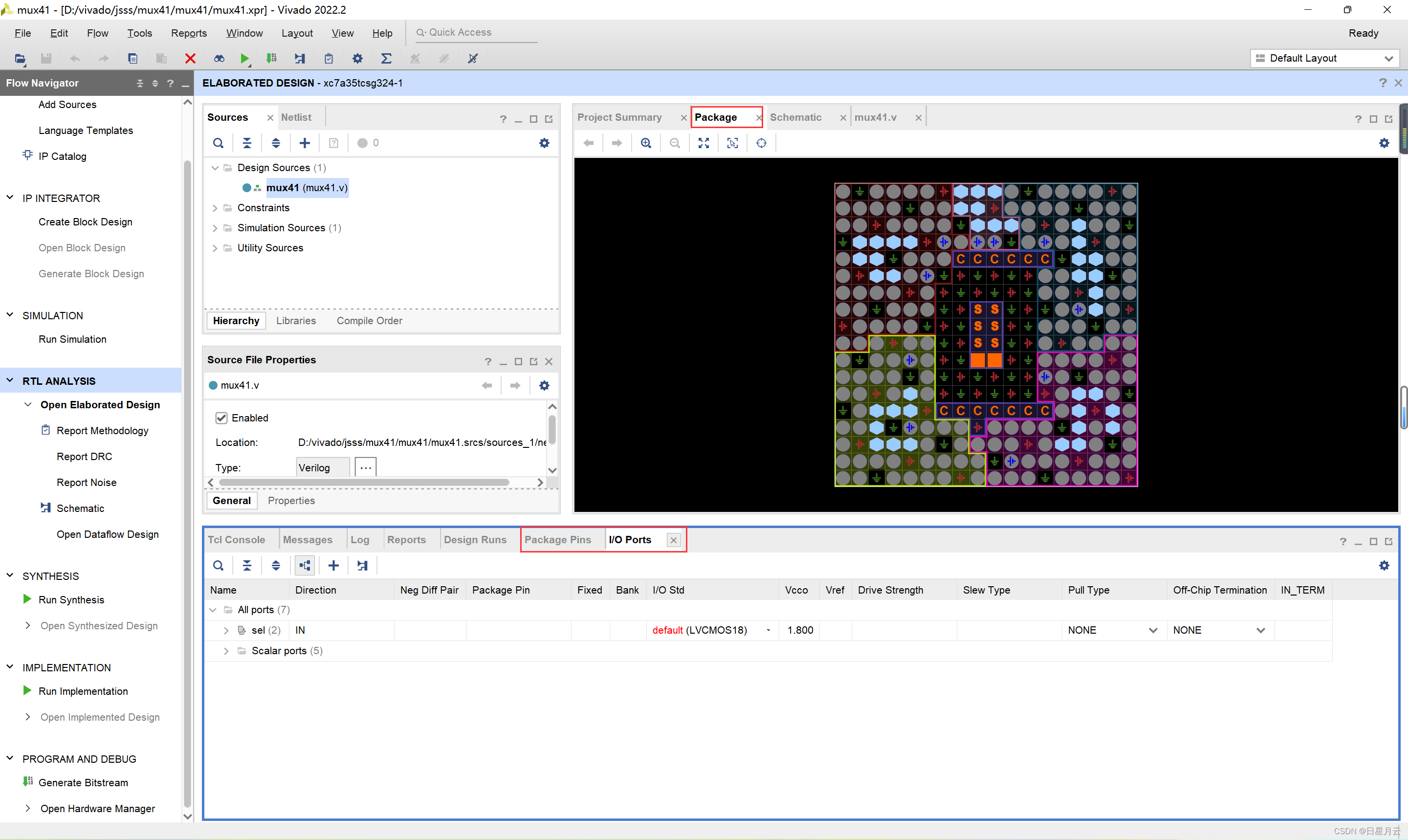

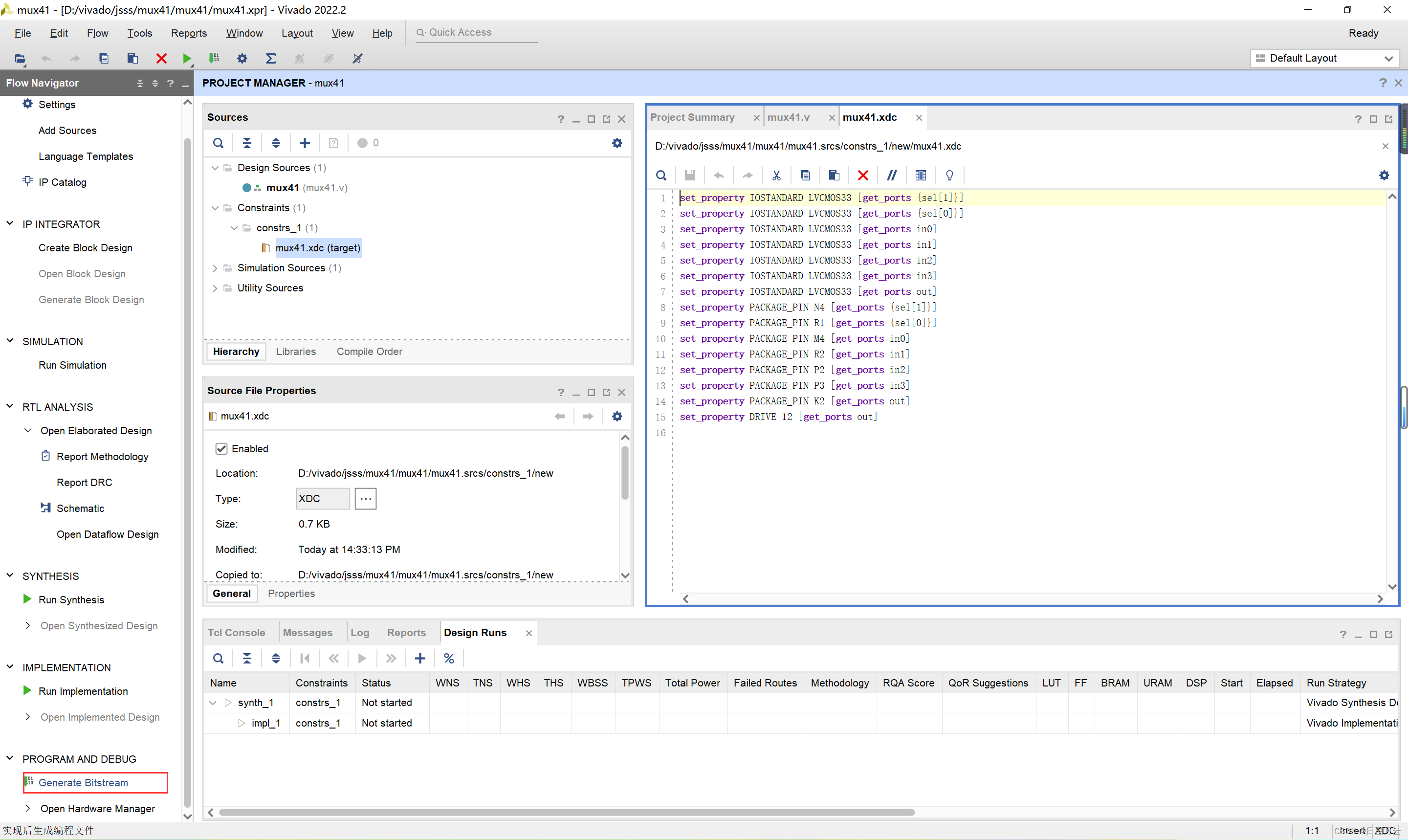

为设计添加约束

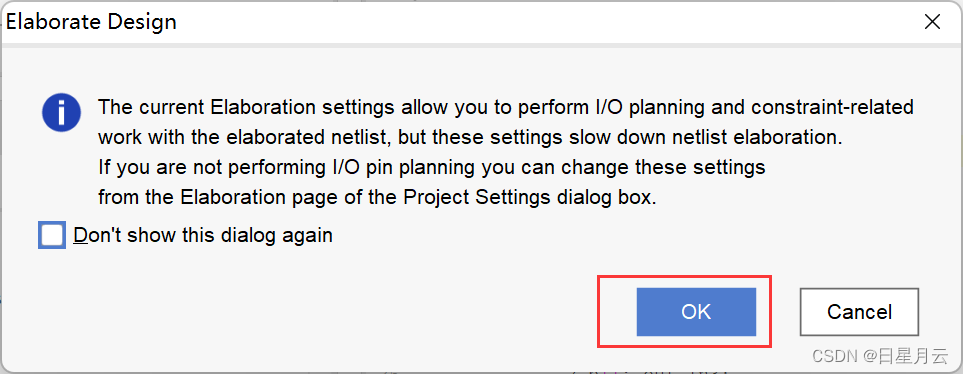

可以通过左边的导航栏中

PTL ANALYSIS

Open Elaborated Design

单击OK

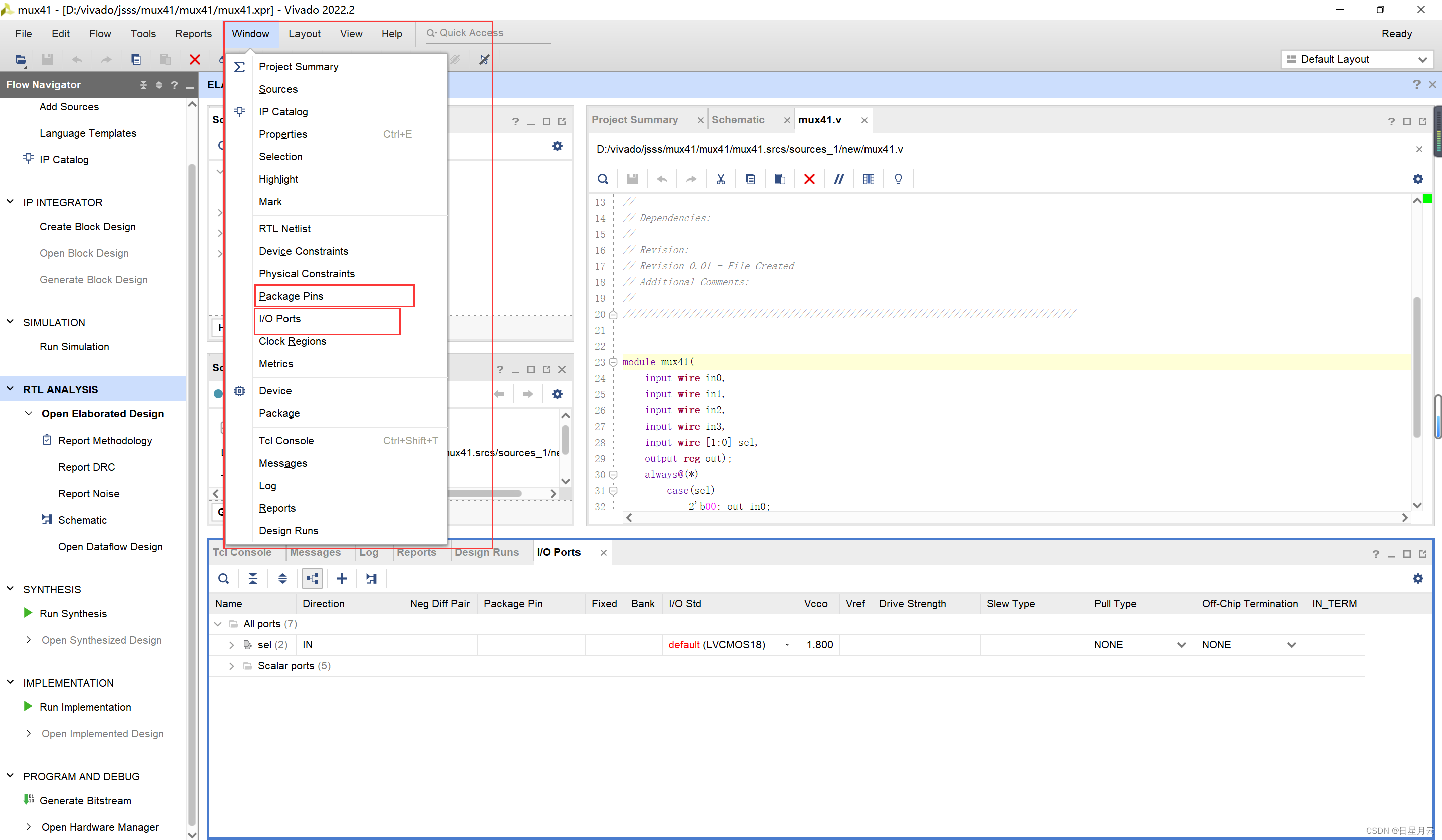

如果没有一些窗口可以在Windows添加显示

这样就可以显示了

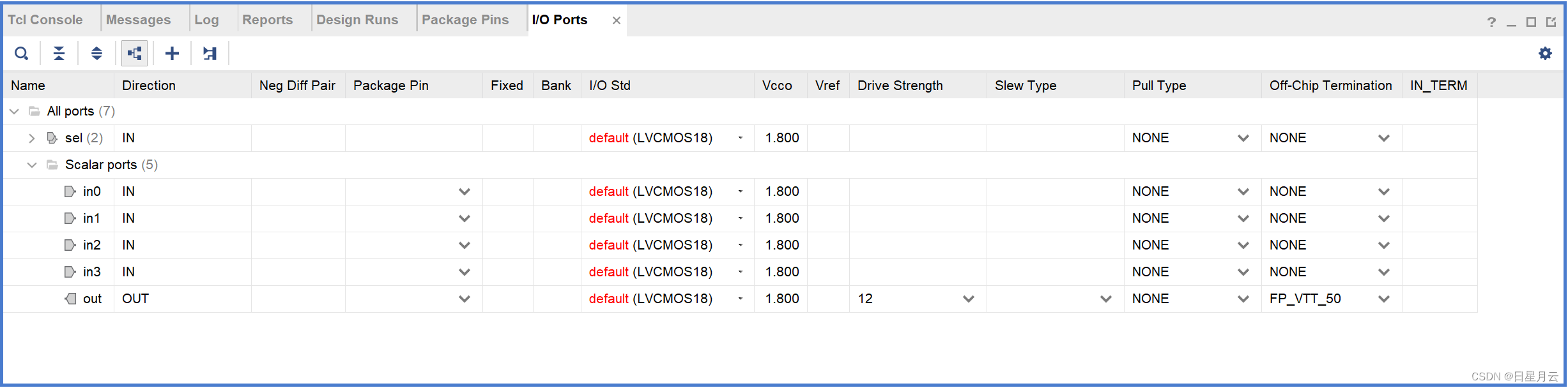

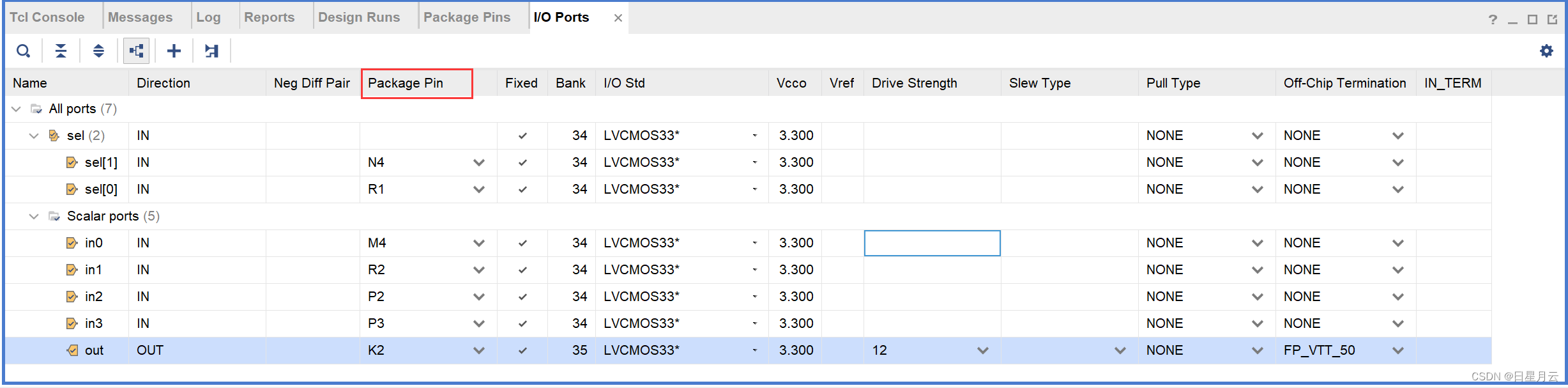

现在开始设置IO Ports

设置I/O Std

设置Package Pin

单击左上方保存

保存约束文件

命名:mux41

可以看见工程中

多了mux41.xdc

双击打开

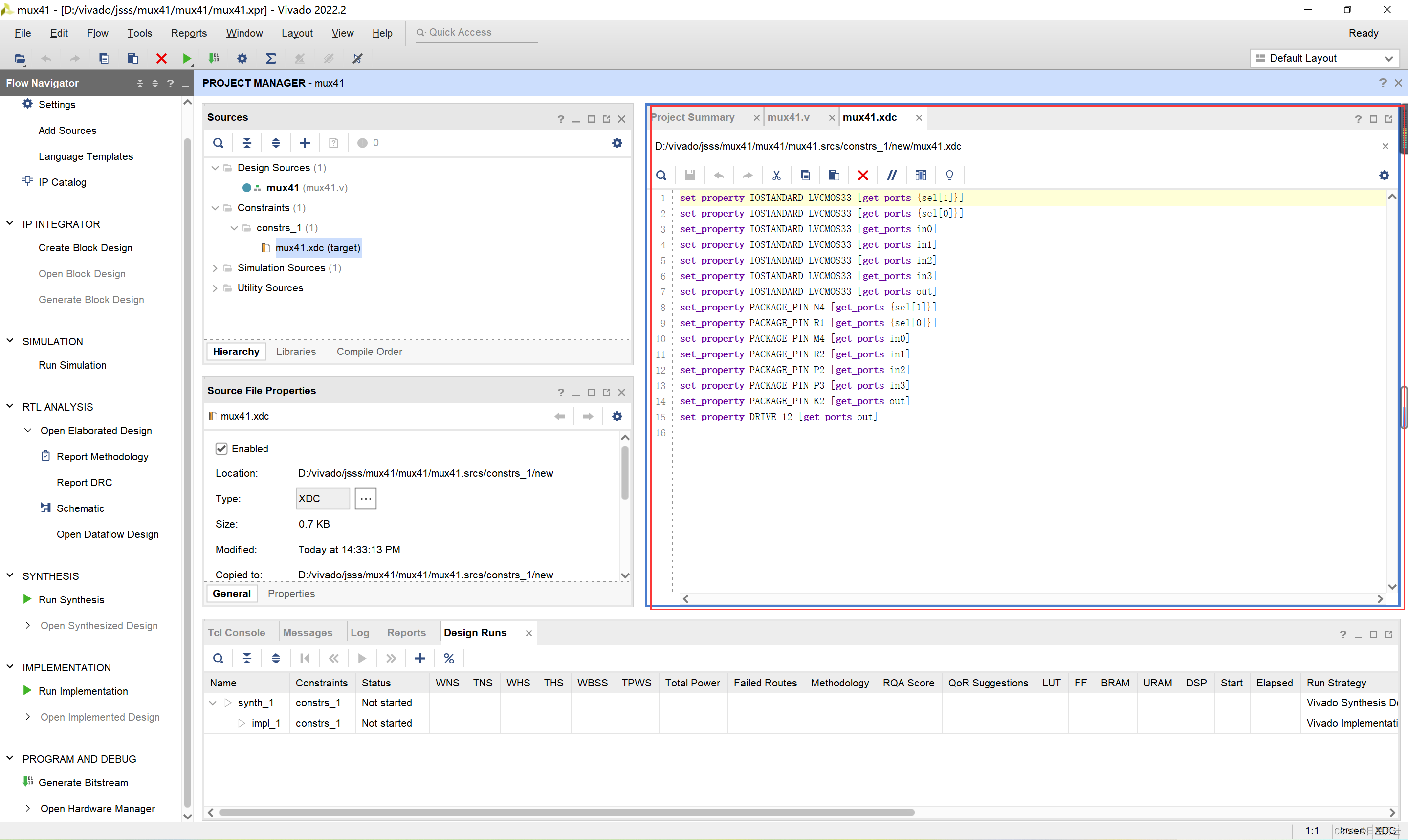

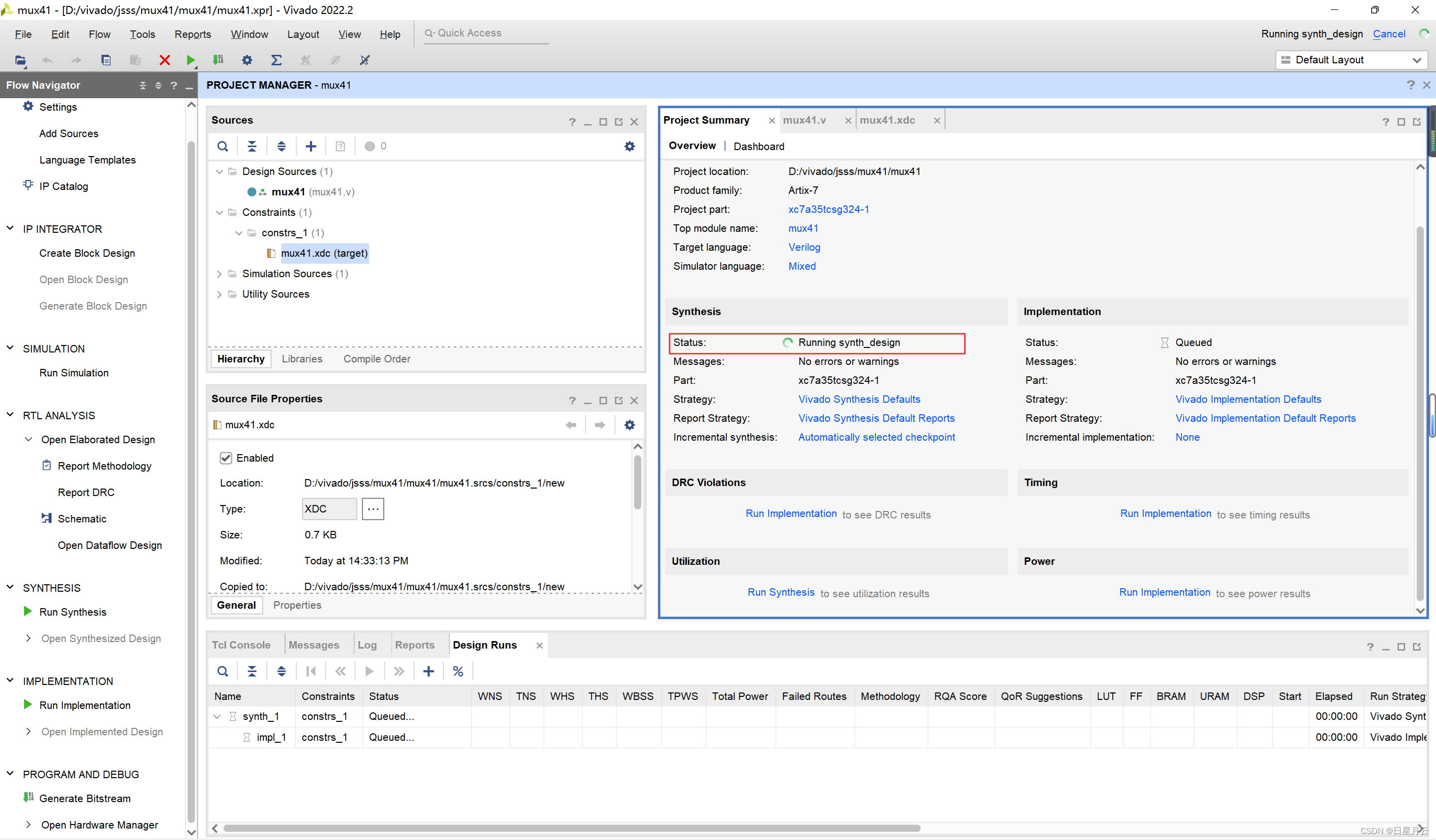

工程的实现

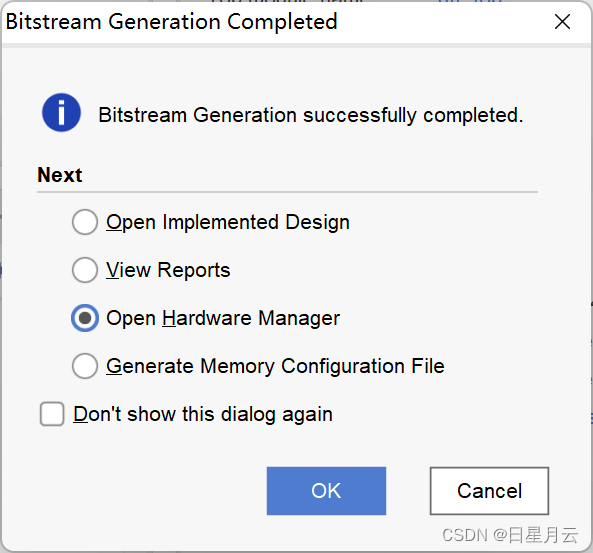

生成2进制码流文件

PROGRAM AND DEBUG

Generate Bitstream

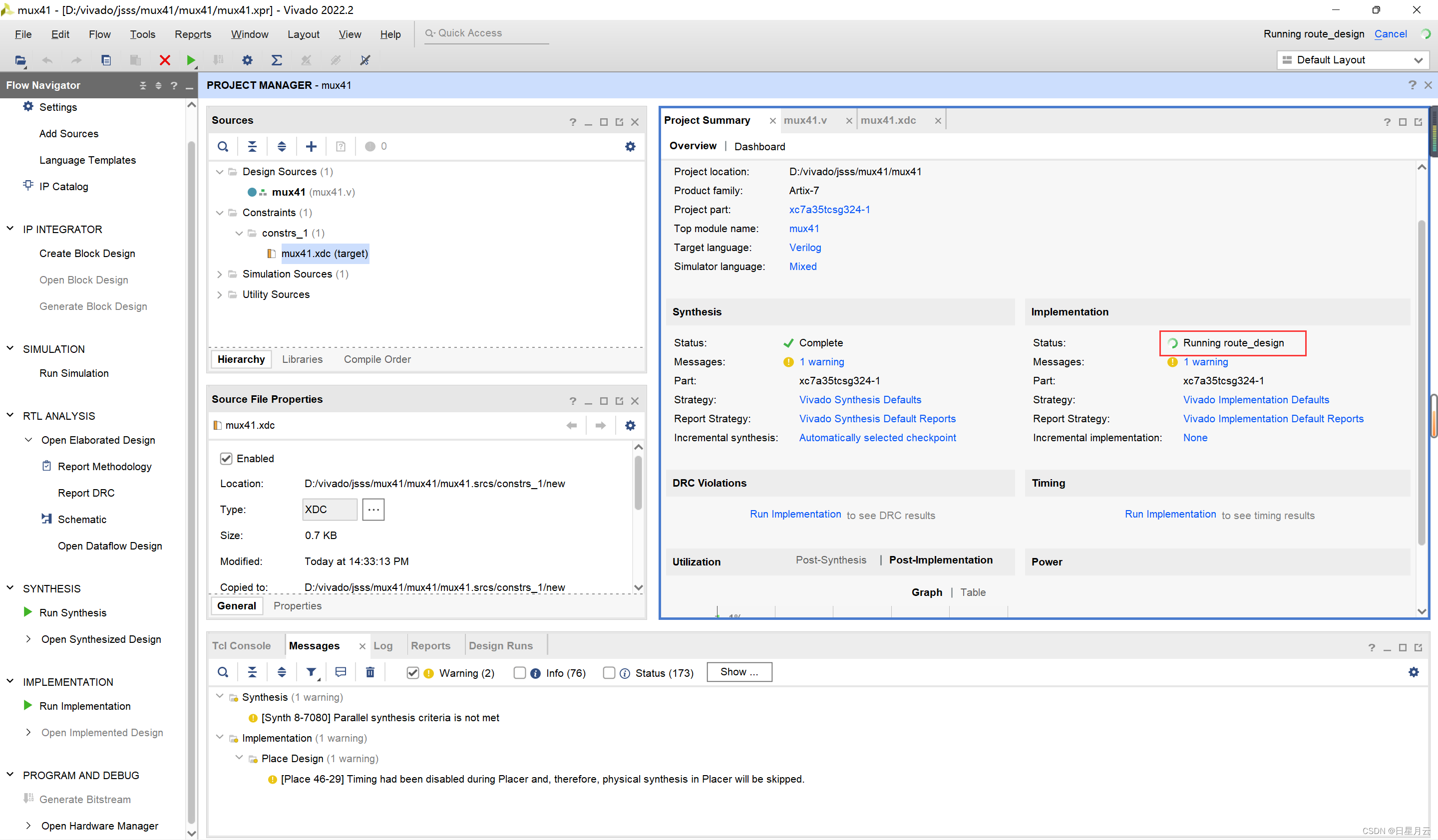

正在对工程进行综合

正在对工程进行实现

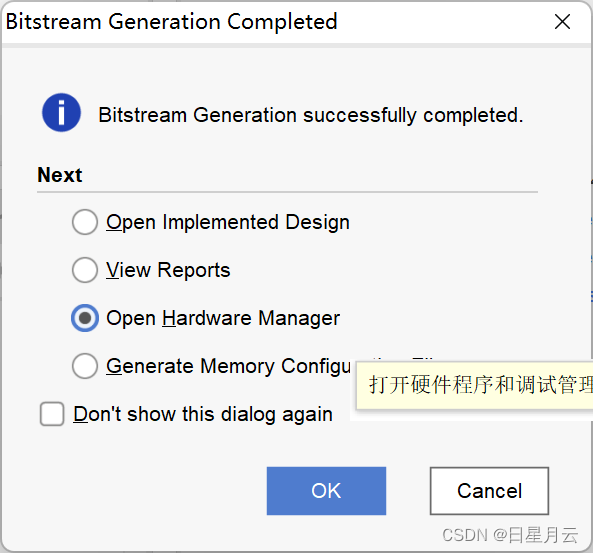

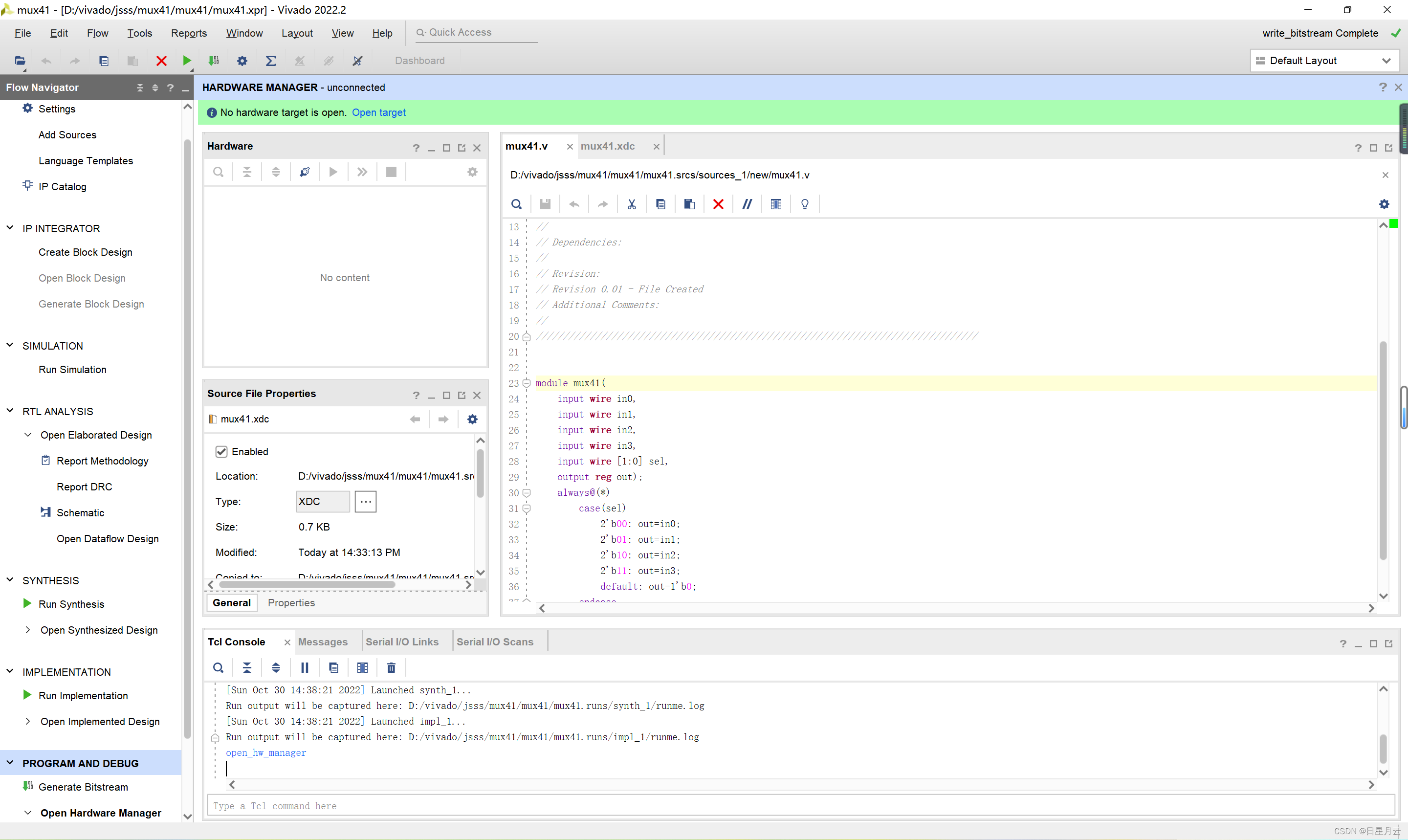

调试

可以在此处打开硬件调试器

或者在导航栏中

PROGRAM AND DEBUG

Open Hardware Manager

打开显示如下

一定要确认PC机和FPGA开发板连接,并且FPGA连接电源

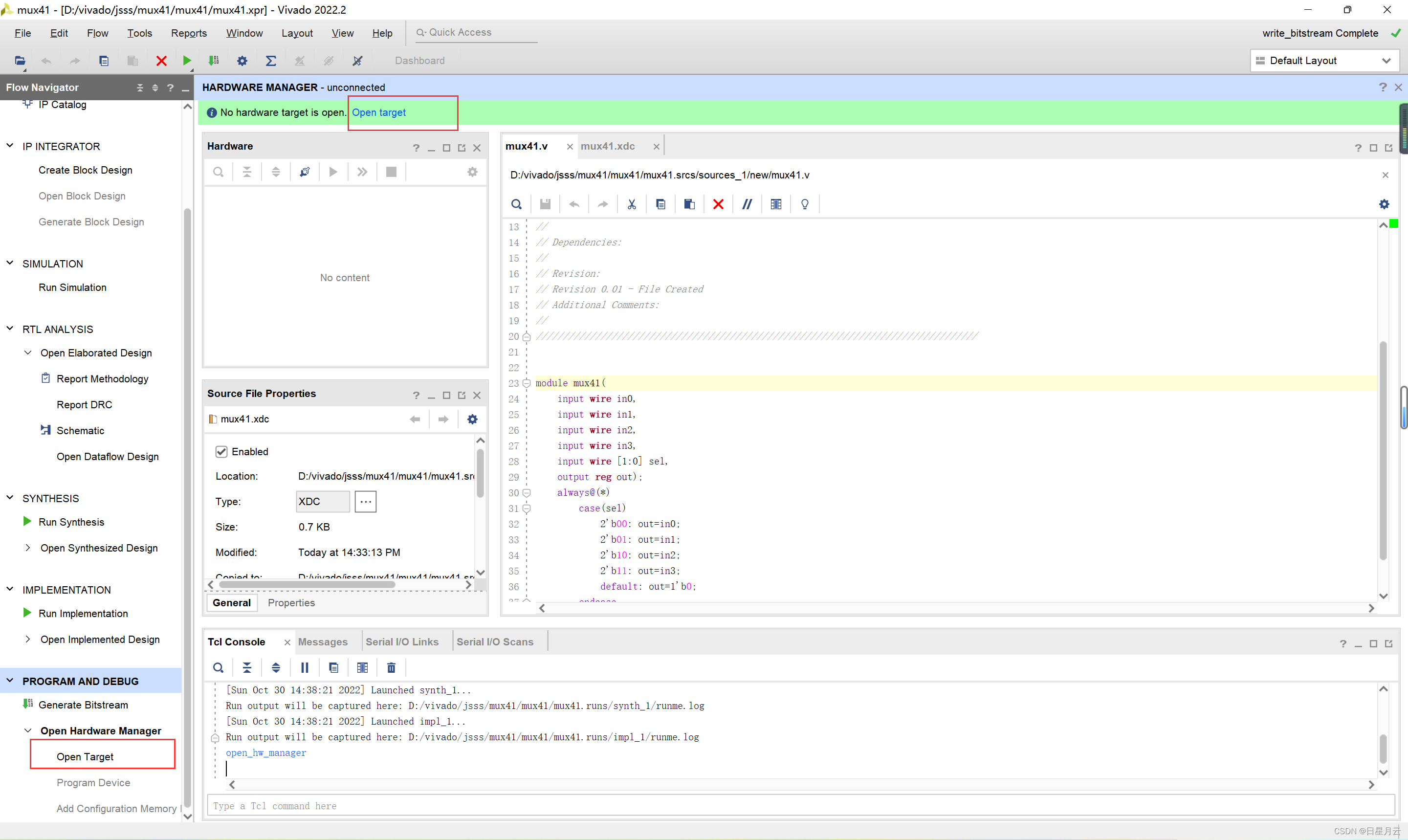

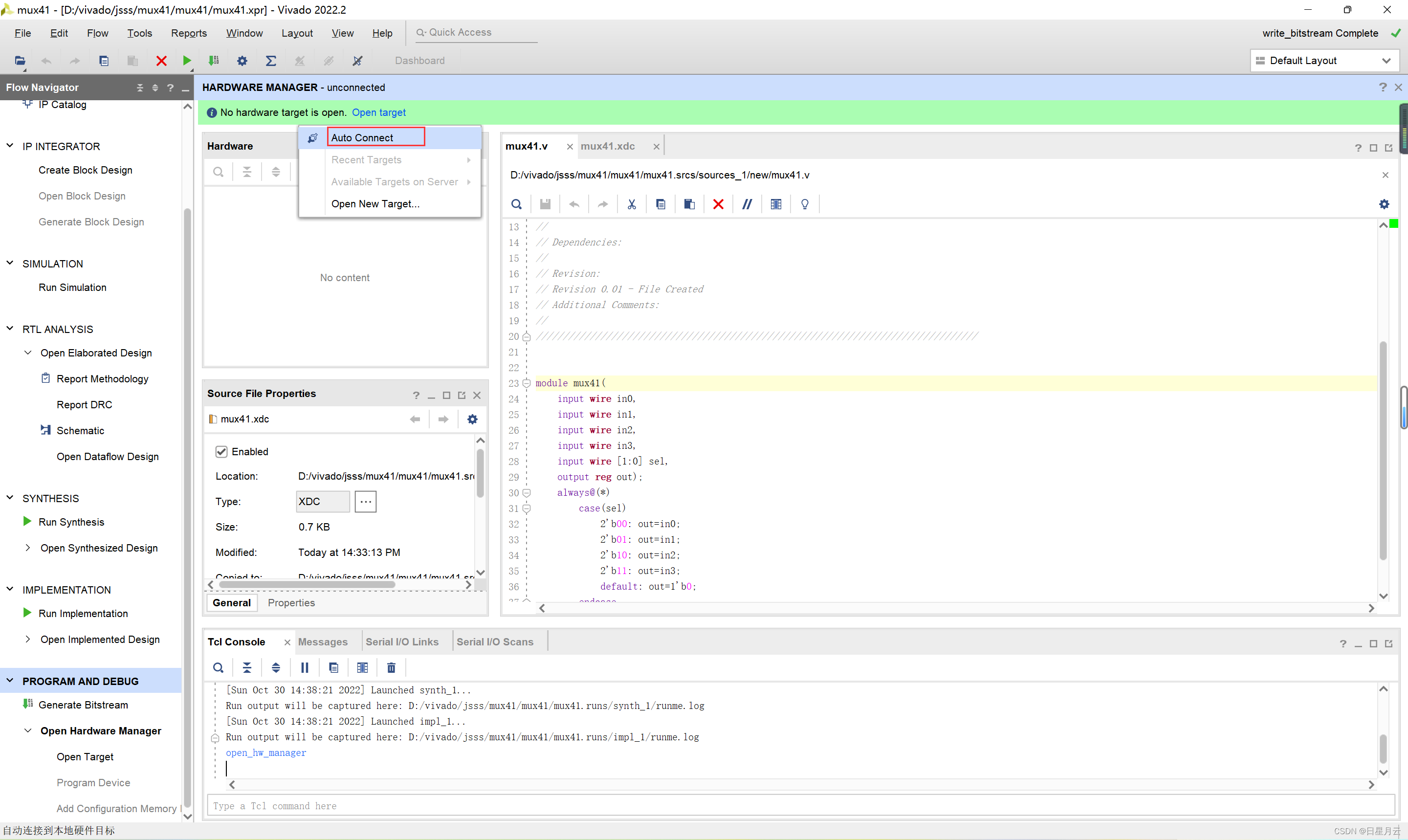

点击Open target

点击 Auto Connect

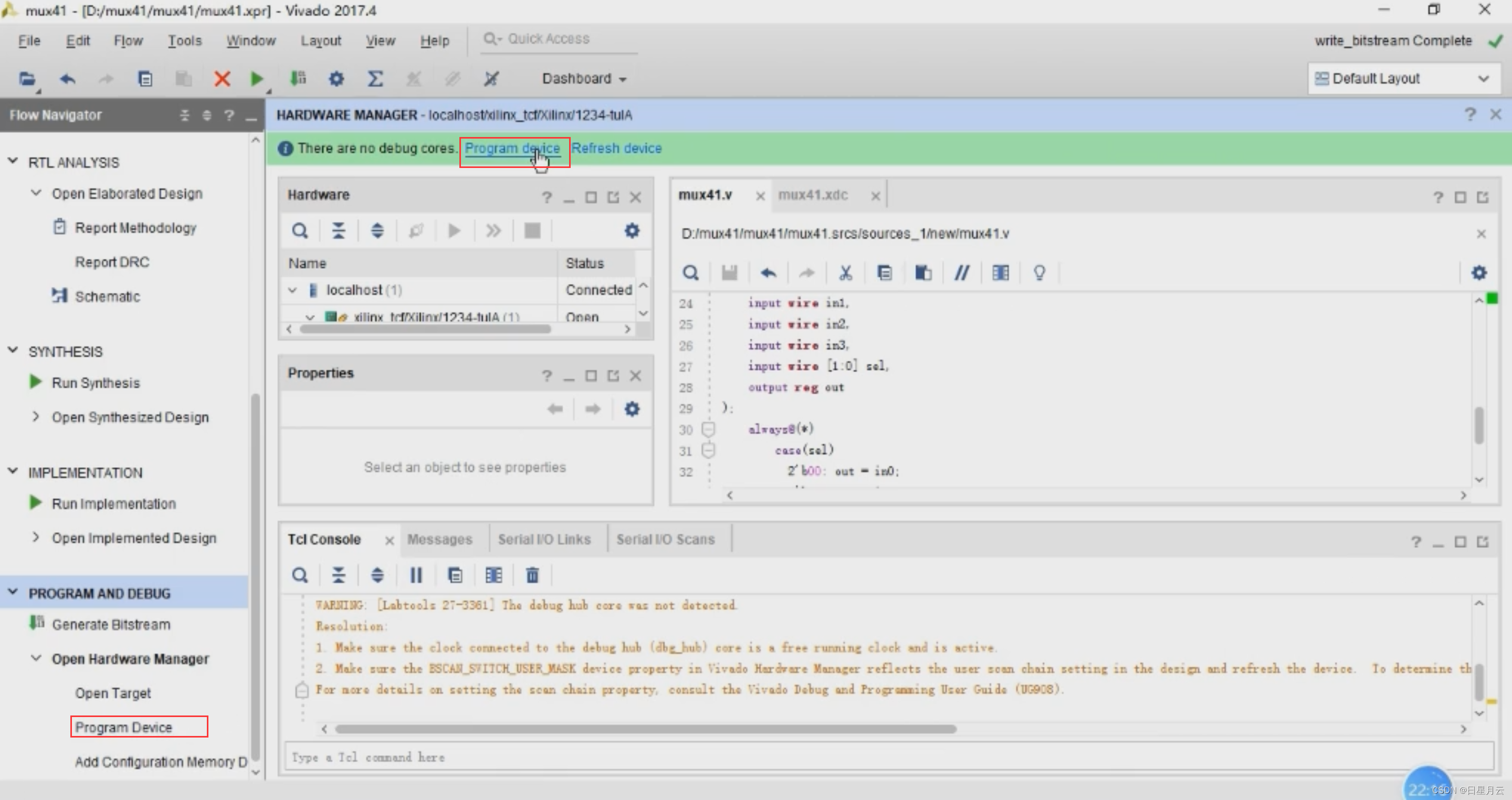

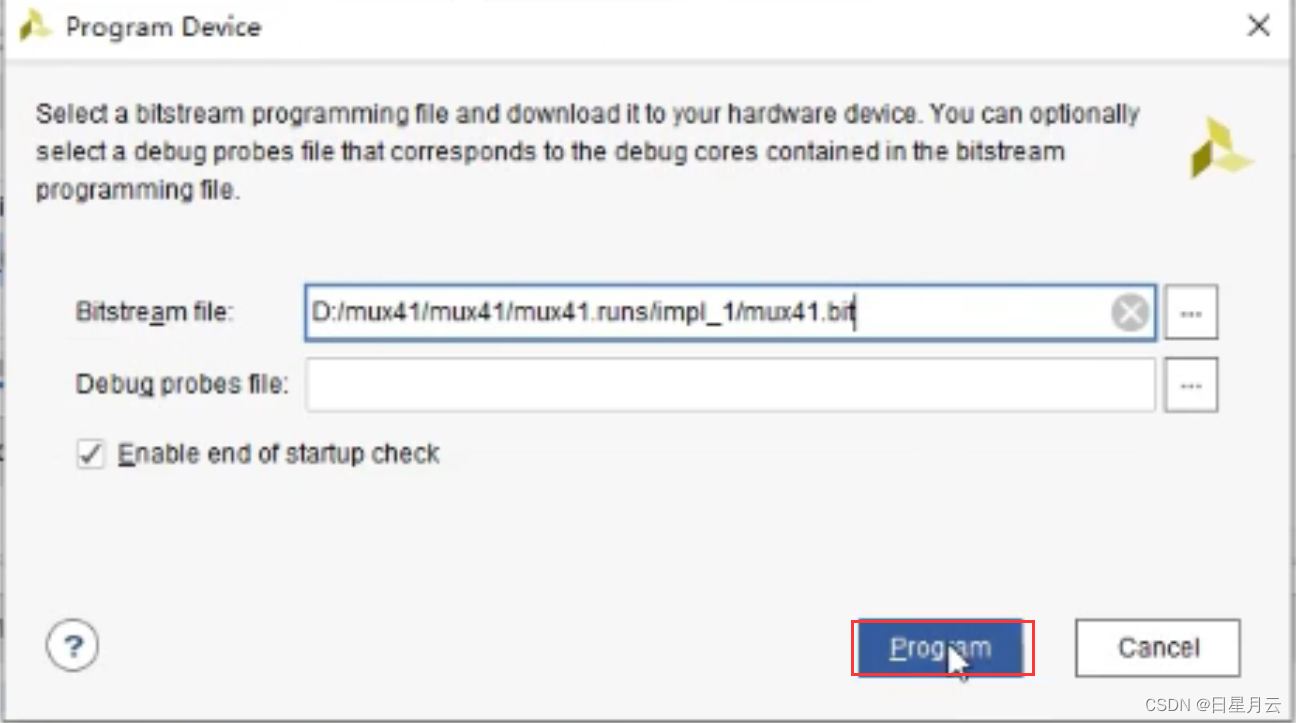

Program device

开发板验证

略

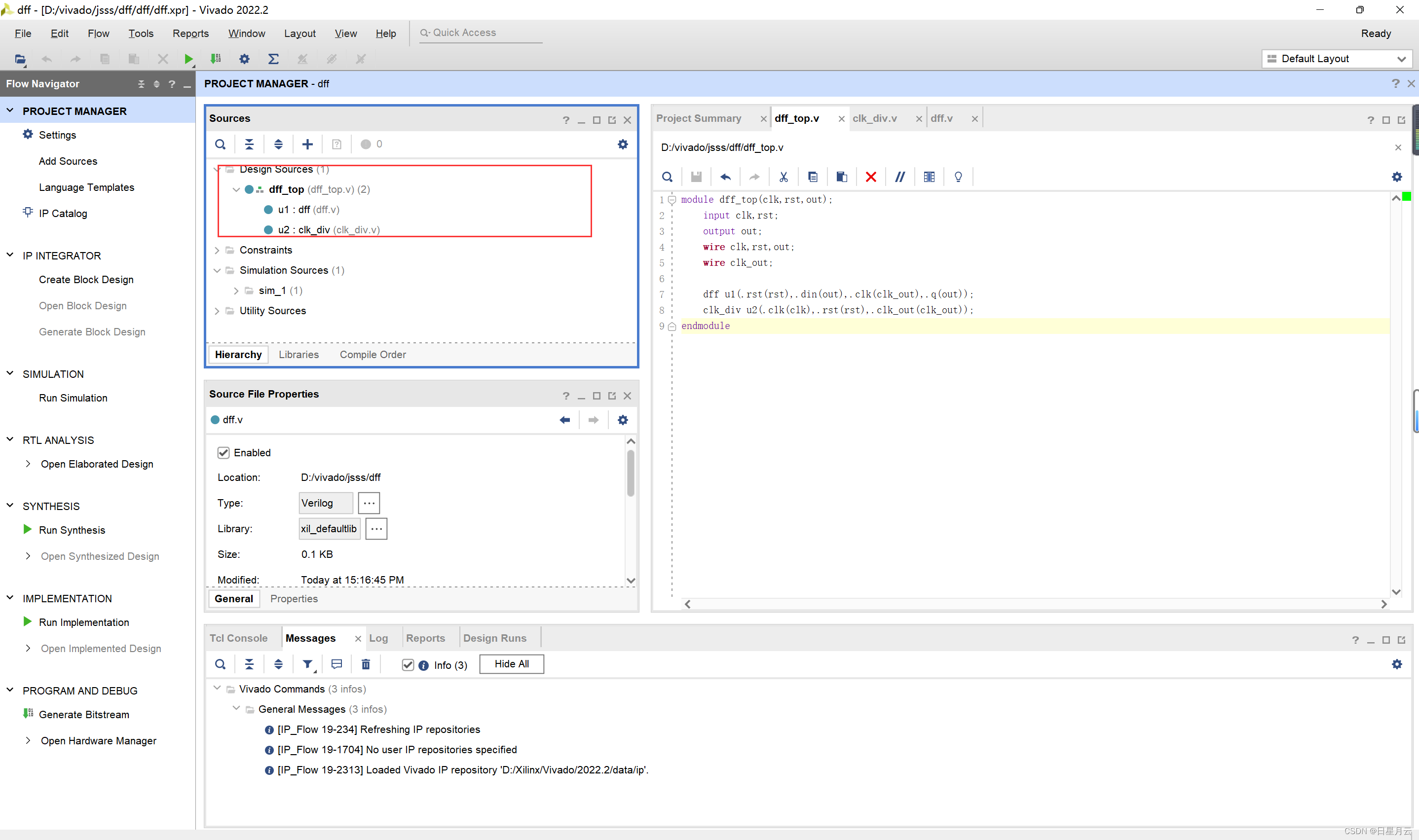

vivado操作时序电路

以D触发器为例

新建工程

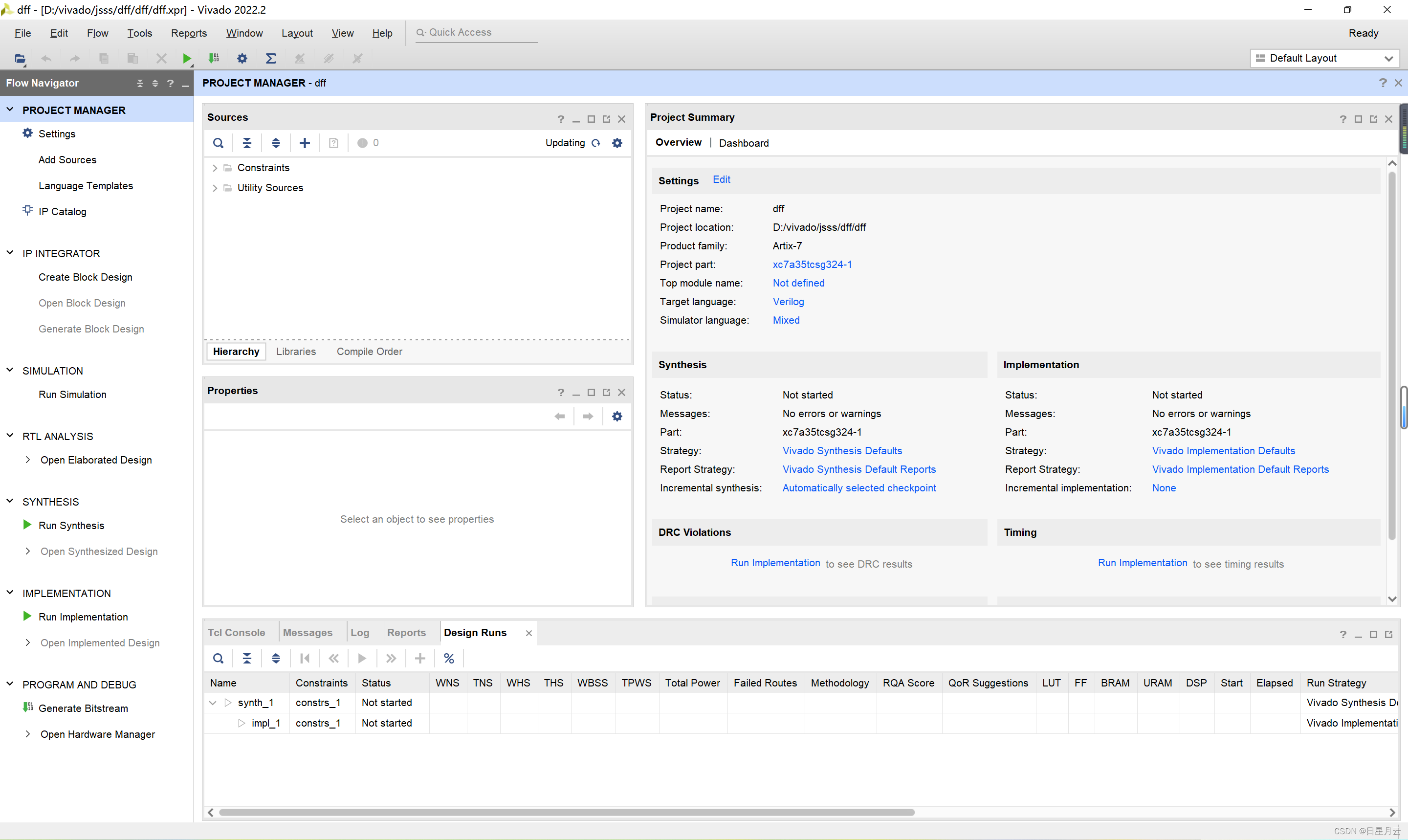

dff

xc7a35tcsg324-1

显示

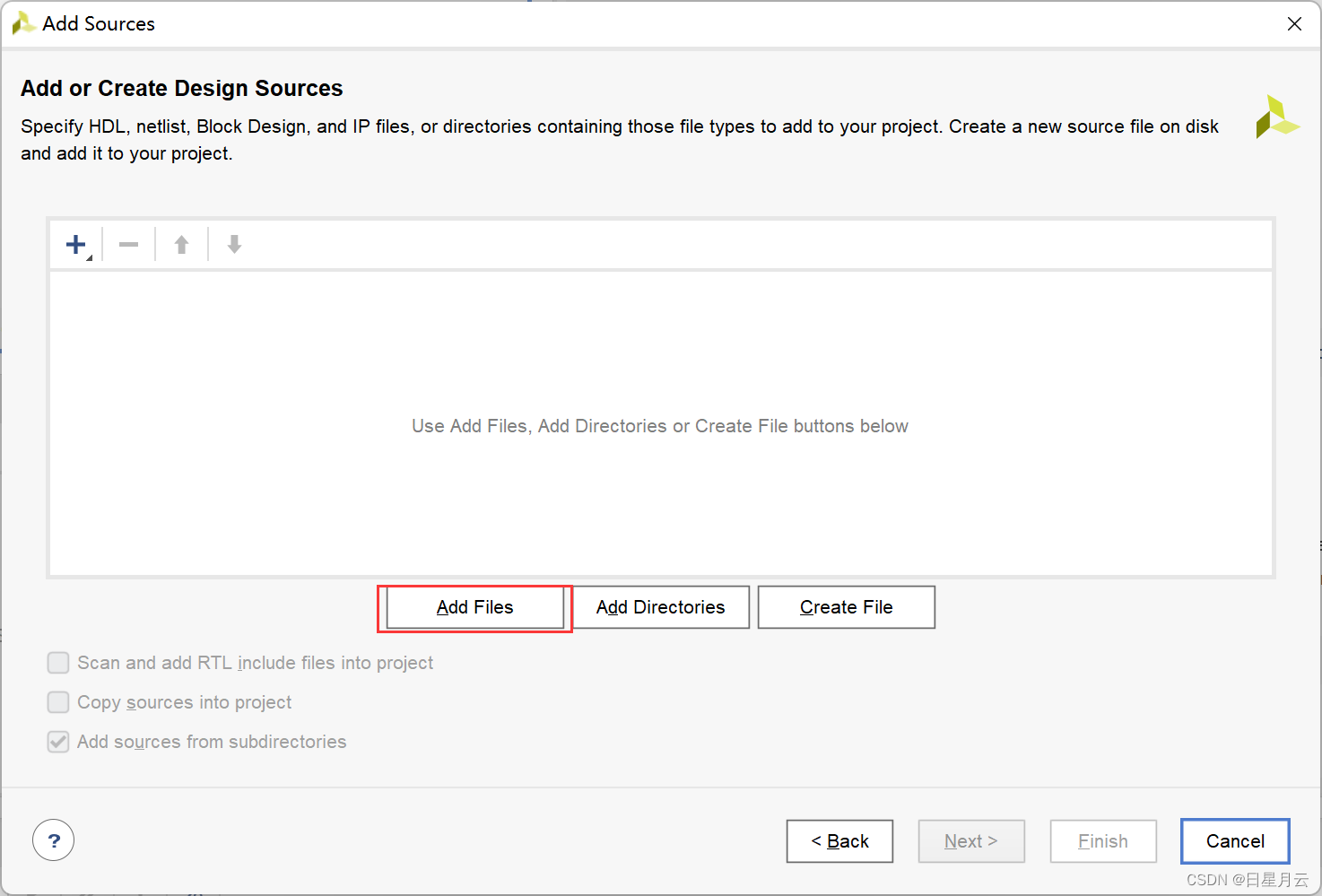

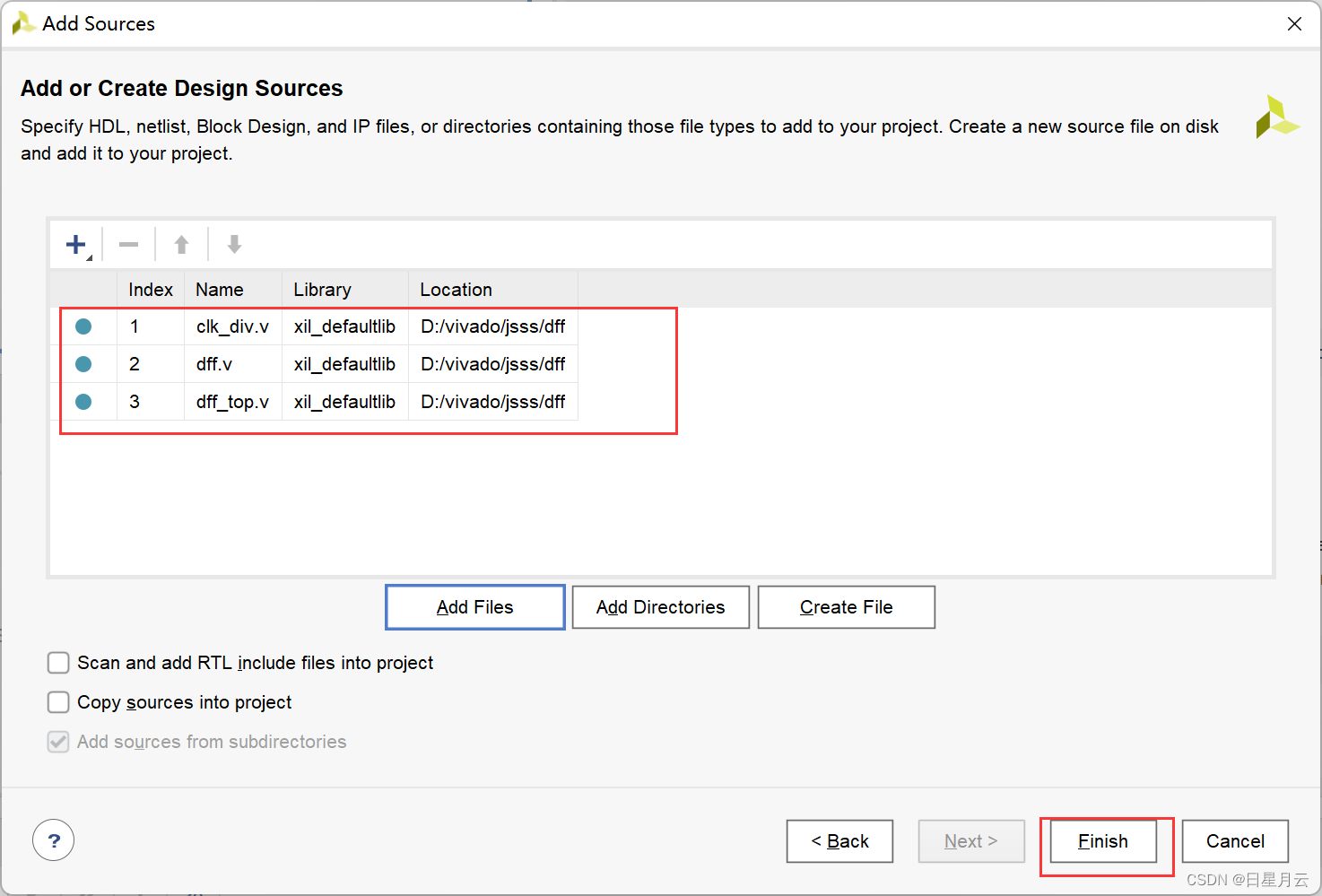

添加源文件

Add Files

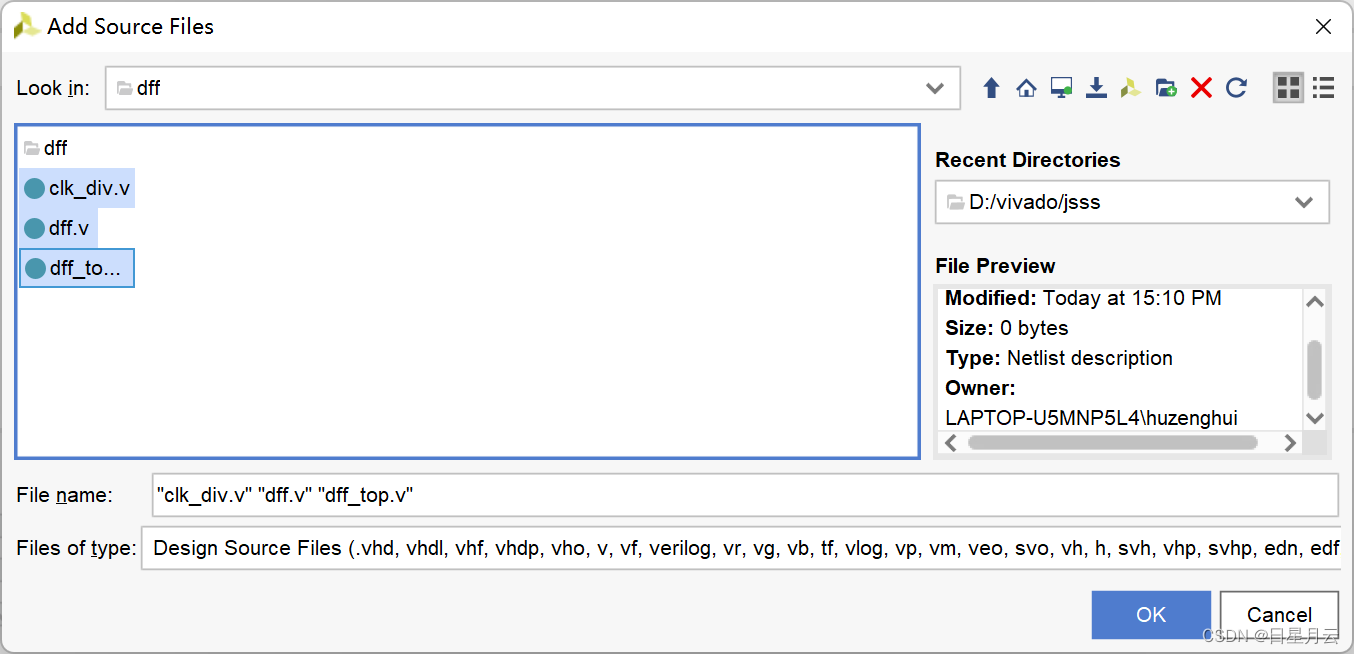

如下三个文件

Add Files

dff_top

module dff_top(clk,rst,out);

input clk,rst;

output out;

wire clk,rst,out;

wire clk_out;

dff u1(.rst(rst),.din(out),.clk(clk_out),.q(out));

clk_div u2(.clk(clk),.rst(rst),.clk_out(clk_out));

endmodule

clk_div

`timescale 1ns/1ns

module clk_div(

input clk,

input rst,

output clk_out

);

reg[13:0] cnt_first,cnt_second;

always @(posedge clk or posedge rst)

if(rst)

cnt_first <= 14'd0;

else if(cnt_first==14'd9999)

cnt_first <= 14'd0;

else

cnt_first <= cnt_first + 1'b1;

always @(posedge clk or posedge rst)

if(rst)

cnt_second <= 14'd0;

else if(cnt_second==14'd10000)

cnt_second <= 14'd0;

else if(cnt_first==14'd9999)

cnt_second <= cnt_second + 1'b1;

assign clk_out= cnt_second==14'd10000 ? 1'b1:1'b0;

endmodule

开发板分频太高

所以需要cnt_div分频模块

100MHz->1Hz

dff

module dff(rst,din,clk,q);

input rst,din,clk;

output q;

reg q;

always @(posedge clk)

if(rst) q<=0;

else q<=~din;

endmodule

显示

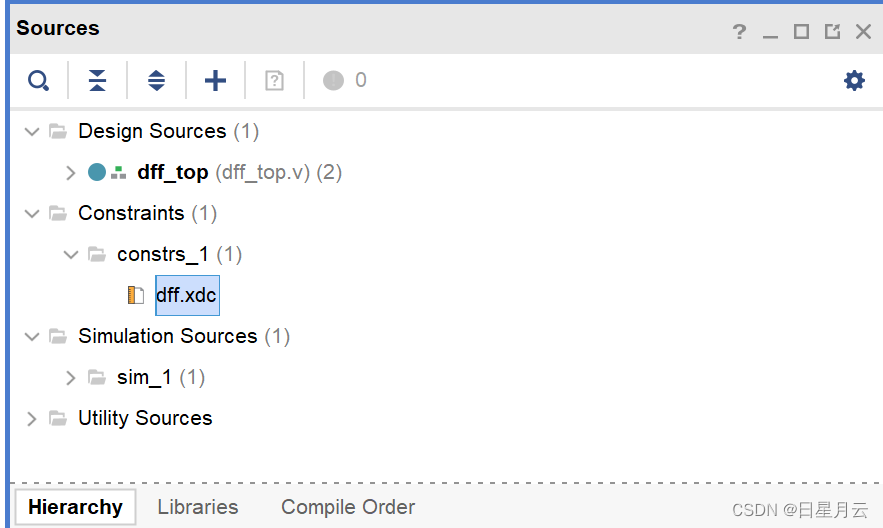

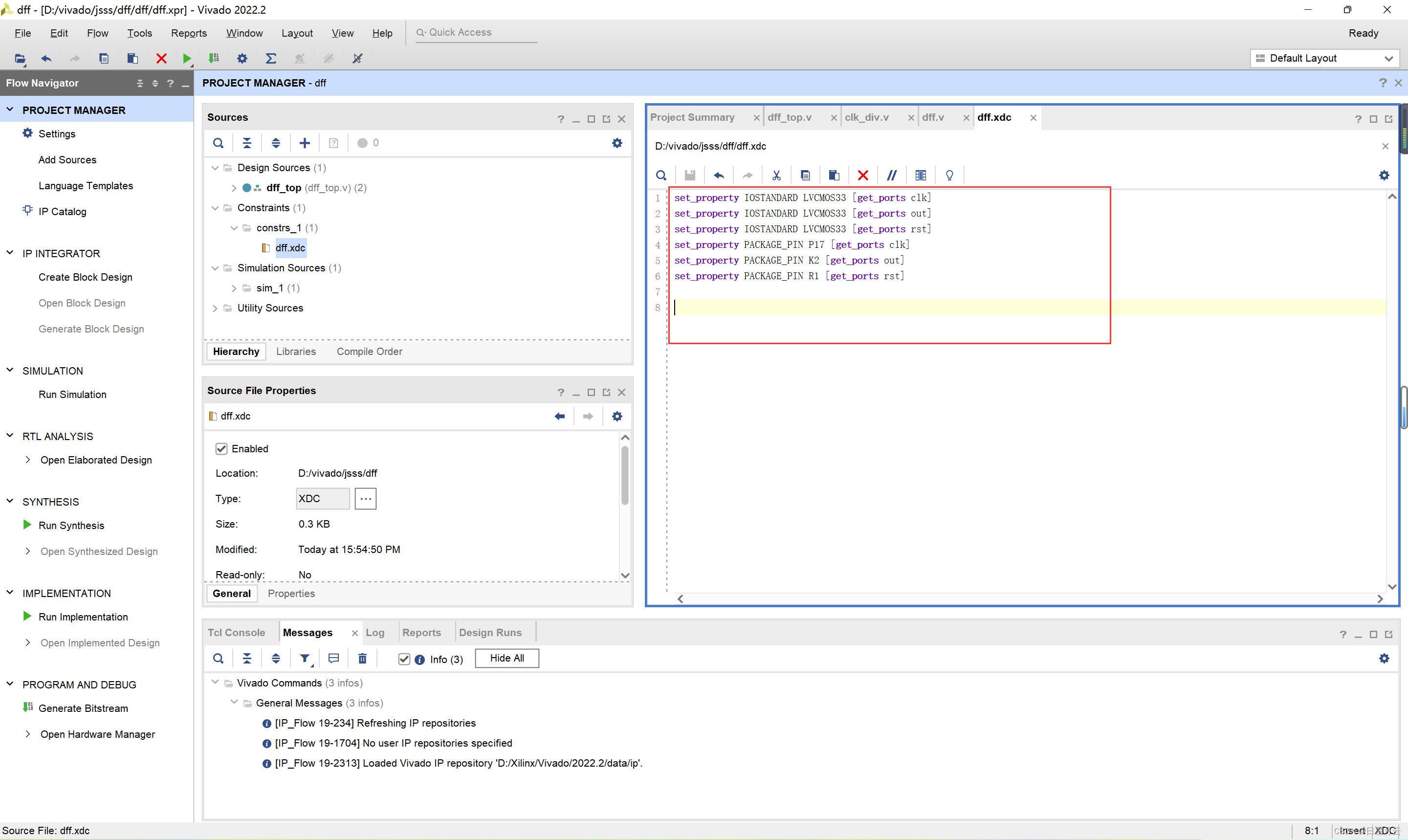

为设计添加约束

Add or create constraints

Add Files

dff.xdc

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports out]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property PACKAGE_PIN P17 [get_ports clk]

set_property PACKAGE_PIN K2 [get_ports out]

set_property PACKAGE_PIN R1 [get_ports rst]

Ok

显示

双击打开

工程的实现

PROGRAM AND DEBUG

Generate Bltstream

Open Hardware Manager

连接FPGA开发板

Open Target

Program Device

开发板演示

略