在过去的十年中,半导体存储器领域最重要的现象是闪存市场的爆炸式增长,其推动力来自手机和其他类型的便携式电子设备。强大的综合技术、灵活性和成本使闪存在大多数非易失性存储器应用中成为一种广泛使用、成熟稳固的技术。如今,闪存的销售额在整个半导体市场中占有相当大的比重。

1、NAND Flash的发展和分类

根据闪存市场需求,一种众所周知的对闪存产品和相关技术进行分类的方法有两大应用领域定义:

-- 代码存储:存储程序或操作系统,并由微处理器或微控制器执行;

-- 数据(或大容量)存储,用于按顺序记录和读取图像、音乐和语音等数据文件。

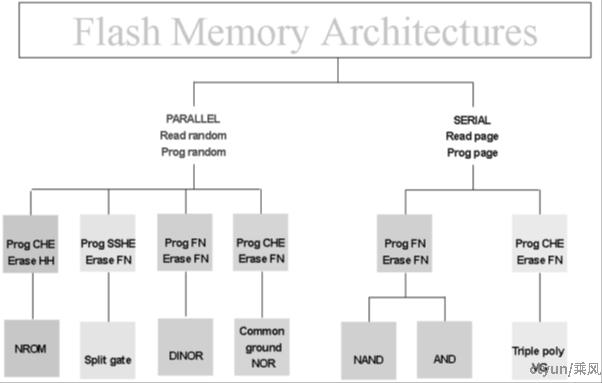

过去曾提出过不同类型的闪存单元和架构。它们可以按存取类型分为并行或串行,也可以按所使用的编程和擦除机制分为Fowler–Nordheim隧道(FN)、沟道热电子(CHE)、热孔(HH)和源侧热电子(SSHE)。在所有这些架构中,目前有两种可被视为行业标准:

一种是通用的 NOR 闪存,由于其多功能性,可同时满足代码和数据存储的需求;

一种是 NAND 闪存,针对数据存储市场进行了优化。

图1是闪存单元结构的家族树,实际的行业标准是 1) 用于代码和数据存储应用的NOR,2) 仅用于数据存储的NAND。本文主要介绍NAND flash相关情况。

图1 闪存单元结构的家族树

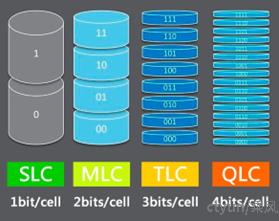

NAND闪存的主要分类以NAND闪存颗粒的技术为主,NAND闪存颗粒根据存储原理分为SLC、MLC、TLC和QLC,从结构上又可分为2D、3D两大类。

第一代SLC(Single-Level Cell)每单元可存储1比特数据(1bit/cell),性能好、寿命长,可经受10万次编程/擦写循环,但容量低、成本高;

第二代MLC(Multi-Level Cell)每单元可存储2比特数据(2bits/cell),性能、寿命、容量、成本各方面比较均衡,可经受1万次编程/擦写循环,现在只有在少数高端SSD中可以见到;

第三代TLC(Trinary-Level Cell)每单元可存储3比特数据(3bits/cell),性能、寿命变差,只能经受3千次编程/擦写循环,但是容量可以做得更大,成本也可以更低,是当前最普及的;

第四代QLC(Quad-Level Cell)每单元可存储4比特数据(4bits/cell),性能、寿命进一步变差,只能经受1000次编程/擦写循环,但是容量更容易提升,成本也继续降低。

目前在SLC、MLC、TLC、QLC闪存颗粒中,TLC已经是主角,QLC是未来发展趋势。QLC颗粒跟前几种颗粒相比最大的优势是价格便宜,容量大,虽然P/E寿命低,但是大容量的优点很好的弥补了这个弱点。TLC又有2D-TLC与3D-TLC两种,目前市面上以3D-TLC居多。3D-TLC又再细分为32层3D-TLC、64层3D-TLC、96层3D-TLC以及最新的128层3D-TLC。

图2 NAND Flash存储方式分类

NAND FLASH 架构虽然最早于1989 年就由日立公司发布了,但基于NAND FLASH 的固态硬盘推广使用是最近这十年来才开始爆发式的增长。

NAND FLASH长久以来其成本一直居高不下,对固态硬盘的推广造成了障碍。3D NAND 技术出现为固态硬盘的成本下降做出了贡献,并且对固态硬盘容量和性能的改进显著。3D NAND FLASH 在比2D NAND 更小的物理空间中提供更高的容量。与2D NAND 相比,3D NAND 可降低每千兆字节的成本,改善电量使用以降低功耗,提高可靠性并提供更高的数据读写性能。随着3D NAND 芯片架构的进步,基于NAND 的闪存设备快速地从消费领域向企业级高性能存储系统领域发展。

2、NAND Flash单元结构

NAND Flash单元通过胞元(cell)来存储信息,胞元基本上是一个浮栅 MOS 晶体管,通过沟道热电子编程,并通过Fowler–Nordheim隧道擦除。闪存的浮动栅 MOS 晶体管,如图3所示,即栅极完全被电介质(即浮动栅极 (FG))包围的晶体管,并由电容耦合控制栅极 (CG) 进行电气控制。由于电绝缘,浮动栅充当胞元器件的存储电极;注入浮动栅的电荷保持在浮动栅上,从而可以调节胞元晶体管的 "表观 "阈值电压(即从控制栅看到的电压)。显然,电介质的质量可以保证不易挥发,而厚度则允许通过电脉冲对胞元进行编程或擦除。浮动栅结构是所有基于浮动栅 MOS 晶体管的非易失性存储器单元的共同结构。

图3 闪存单元的横截面示意图

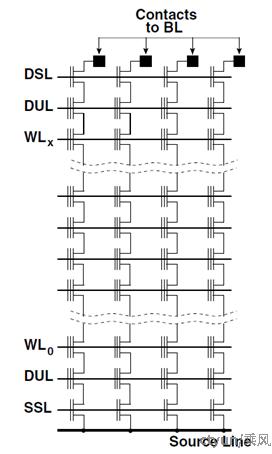

主流的平面闪存阵列由浮栅晶体管的规则排列组成,示意图如图4所示。这些晶体管代表了阵列中以浮动栅极电荷形式存储信息的存储元件,它们沿串串联,并由沿正交方向运行的共享字线(WL)驱动。WL 由高掺杂多晶硅或金属制成,充当晶体管的控制栅极。

图4 NAND flash阵列架构

3、NAND Flash读写操作

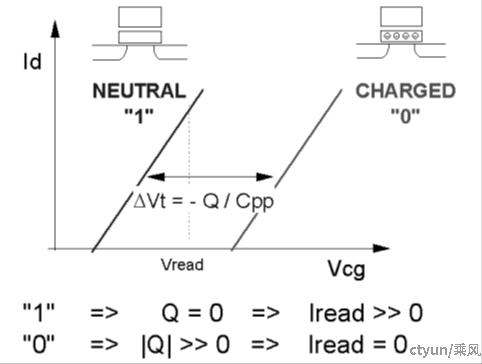

3.1 读取操作

可以通过测量 FG MOS 晶体管的阈值电压来确定闪存单元中存储的数据。最好、最快的方法是读取固定栅极偏置下电池驱动的电流。事实上,如图5所示,在电流-电压平面上,逻辑 "1 "和 "0 "的两个单元表现出相同的跨导曲线,但它们的偏移量--阈值电压偏移(VT)--与存储的电子电荷成正比。因此,一旦确定了适当的电荷量和相应的VT,就可以固定读取电压,使 "1 "单元的电流非常大(在数十微安培的范围内),而 "0 "单元的电流在微安培量级上为零。因此,逻辑状态 "1 "从微观角度可以定义为 FG 中不存储电子电荷(或正电荷),从宏观角度可以定义为读取电流大。反之亦然,逻辑状态 "0 "则分别由存储在 FG 中的电子电荷和零读取电流来定义。

图5 浮栅 MOSFET 读取操作

3.2 写入操作

写入一个 FG 单元的问题与迫使电子超过或穿过能垒的物理问题相对应。这个问题可以利用不同的物理效应来解决。图6概括了用于写入 FG 存储单元的三种主要物理机制。

图6 浮动栅器件的写入机制

CHE 机制:由于源极和漏极之间晶体管沟道中的电场作用,电子获得足够的能量通过氧化硅能垒。事实上,电子能量分布在高能量侧呈现出一个尾部,可由纵向电场调制。

光电效应:即电子通过与能量大于势垒本身的光子相互作用,获得足够的能量来克服势垒。对于二氧化硅来说,这相当于紫外线辐射。EPROM 产品最初就是利用这种机制来擦除整个设备的。

Fowler–Nordheim电子隧道:是一种由电场诱导的量子机械隧道。在薄氧化物上施加强电场(范围在 8-10 MV/cm 之间),可以在不破坏其介电特性的情况下迫使大量电子隧穿电流通过氧化物。

NAND闪存单元通过在漏极一侧的 FG 中注入 CHE 进行编程,并通过 FN 电子穿过隧道氧化物从 FG 到硅表面进行擦除,如图7所示。

图7 NAND闪存写入机制