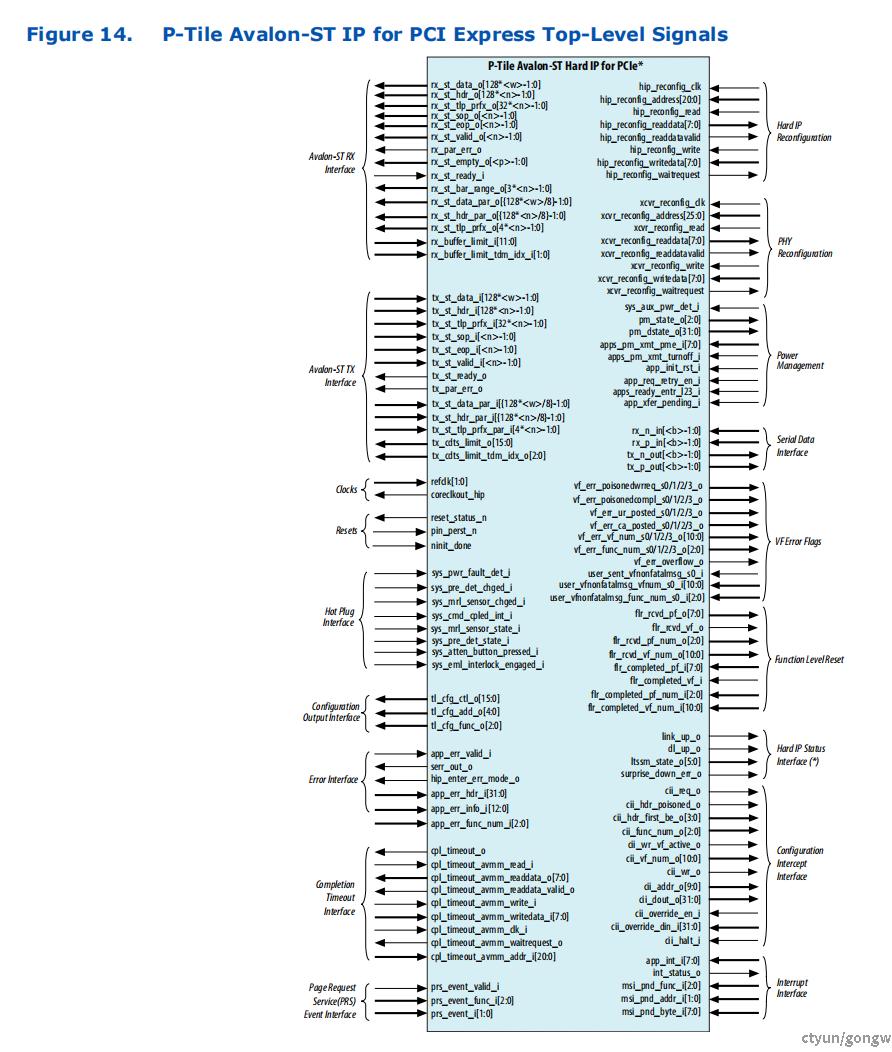

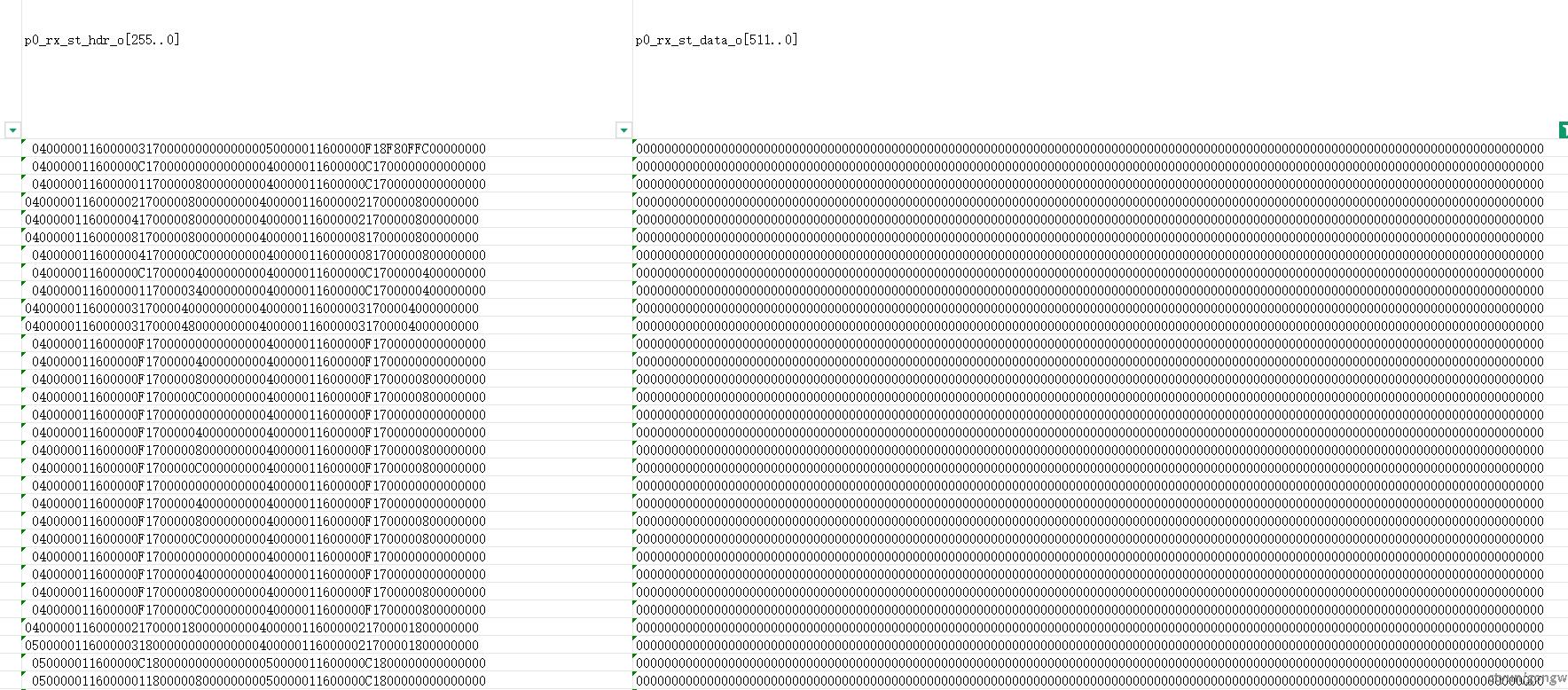

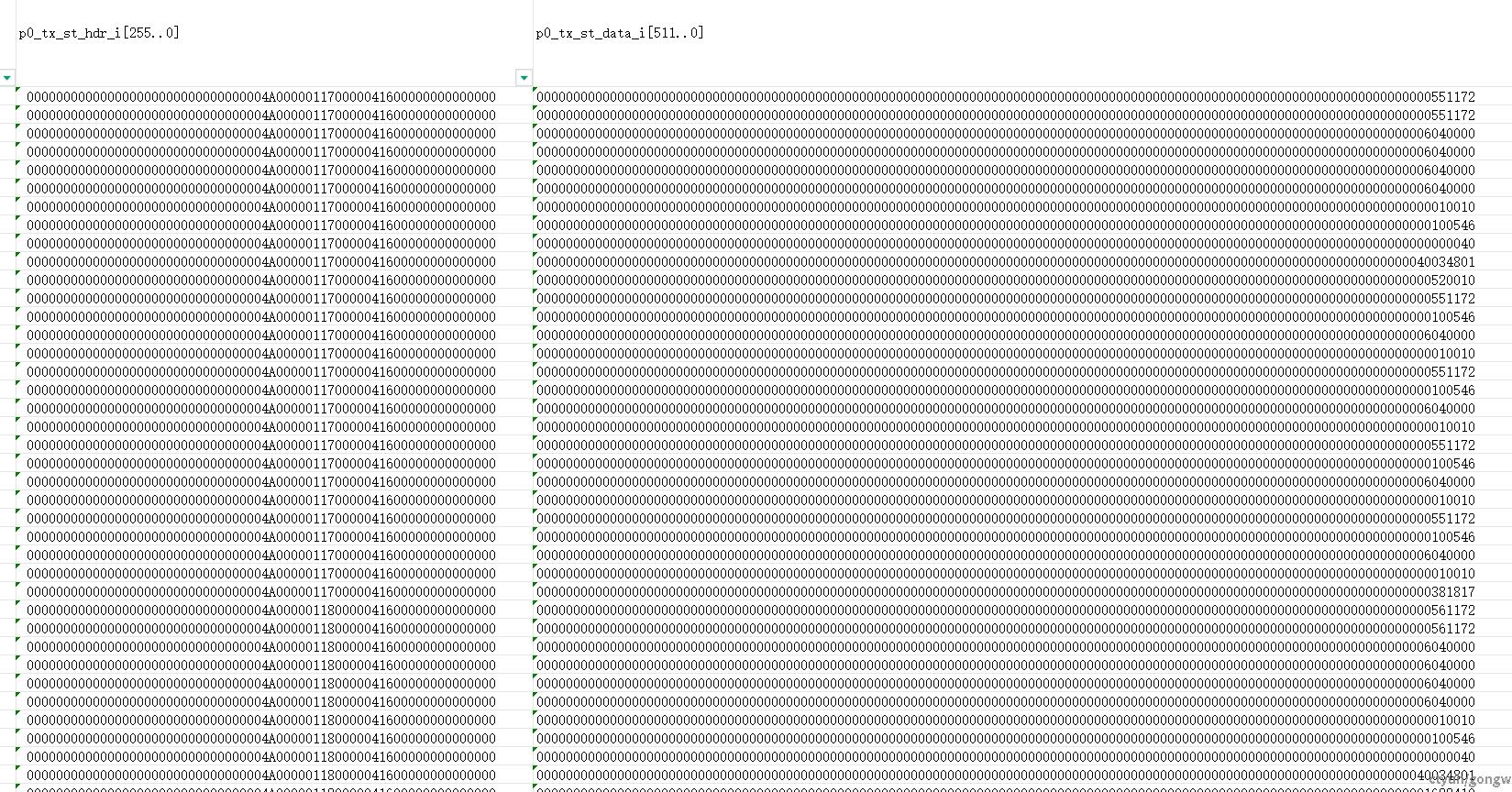

当它配置为TLP Bypass Mode时候,通过抓取其 Avalon-ST RX Interface和 Avalon-ST TX Interface的hdr和data数据信号,

便可以得到基本的PCIe TLP报文内容。通过手动解析或脚本解析,便可以对其进行分类,观察分析FPGA和HOST的TLP交互过程。

The P-Tile Avalon-ST IP for PCIe includes a TLP Bypass mode for both downstream and

upstream ports to allow the implementation of advanced features such as:

• The upstream port or the downstream port of a switch.

• A custom implementation of a Transaction Layer to meet specific user

requirements.

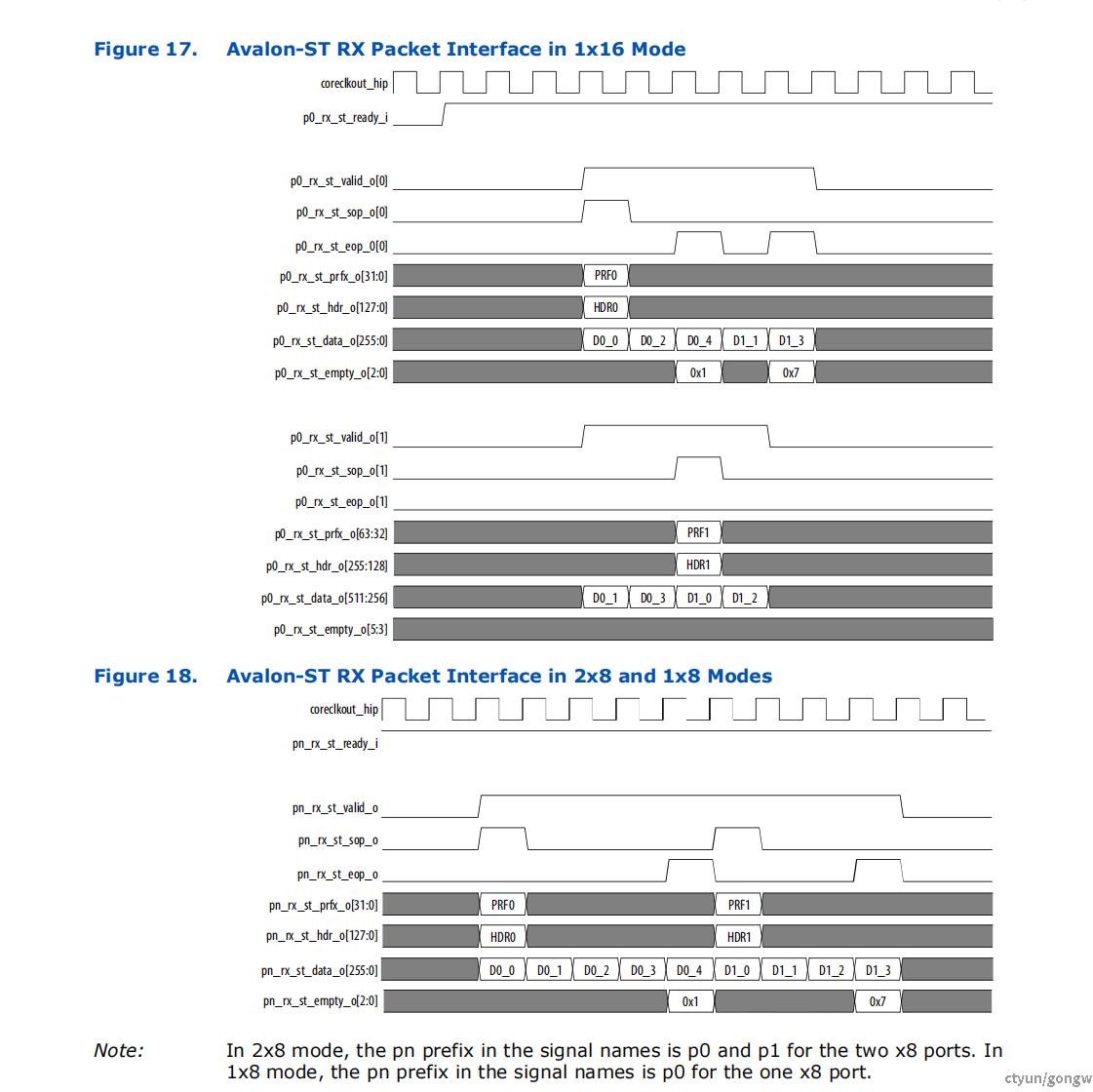

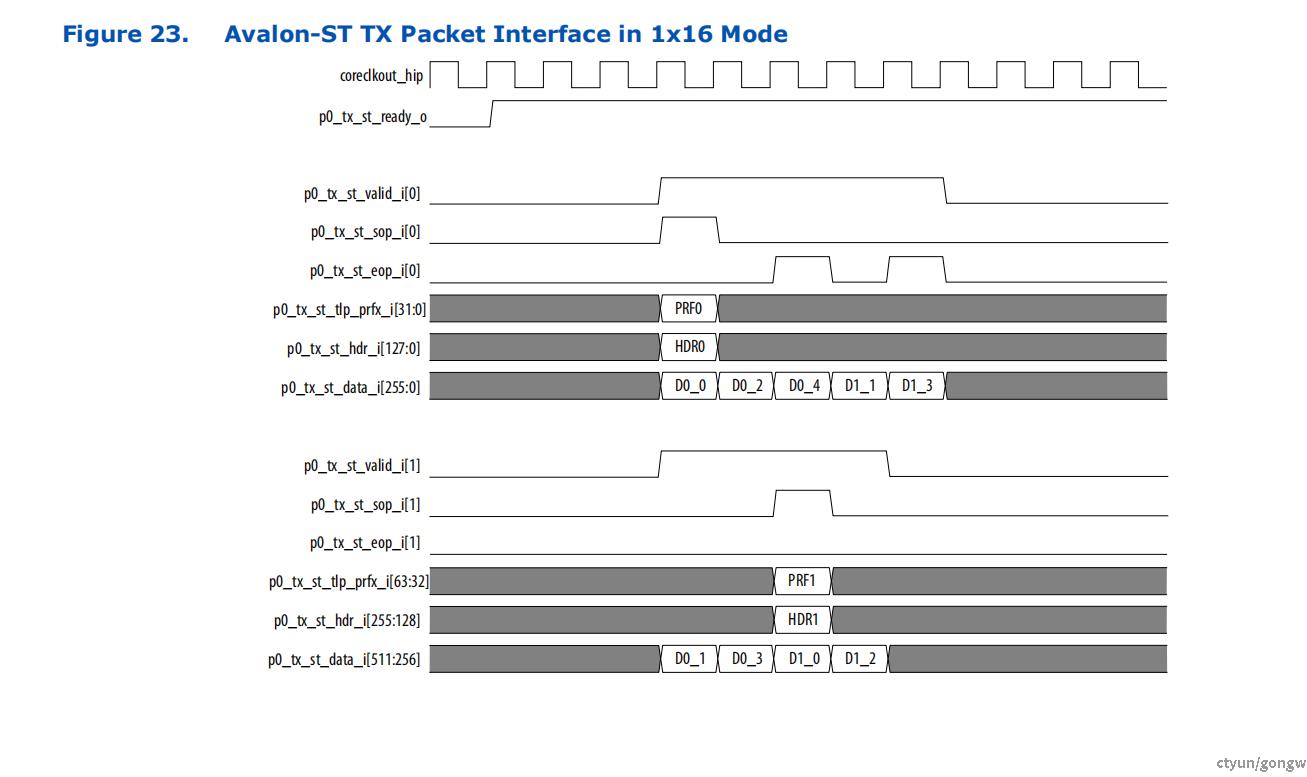

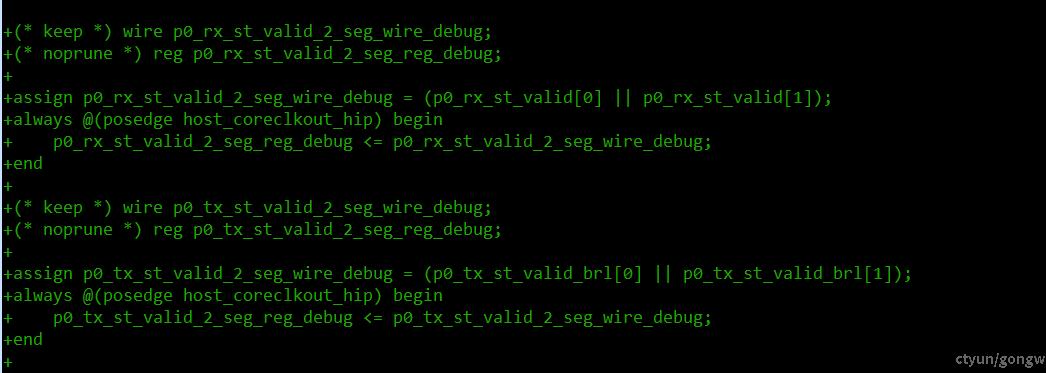

其中hdr和data在x16lane模式下,可以包含2个segment。需要自己在FPGA代码中对2个segment的valid添加逻辑号。

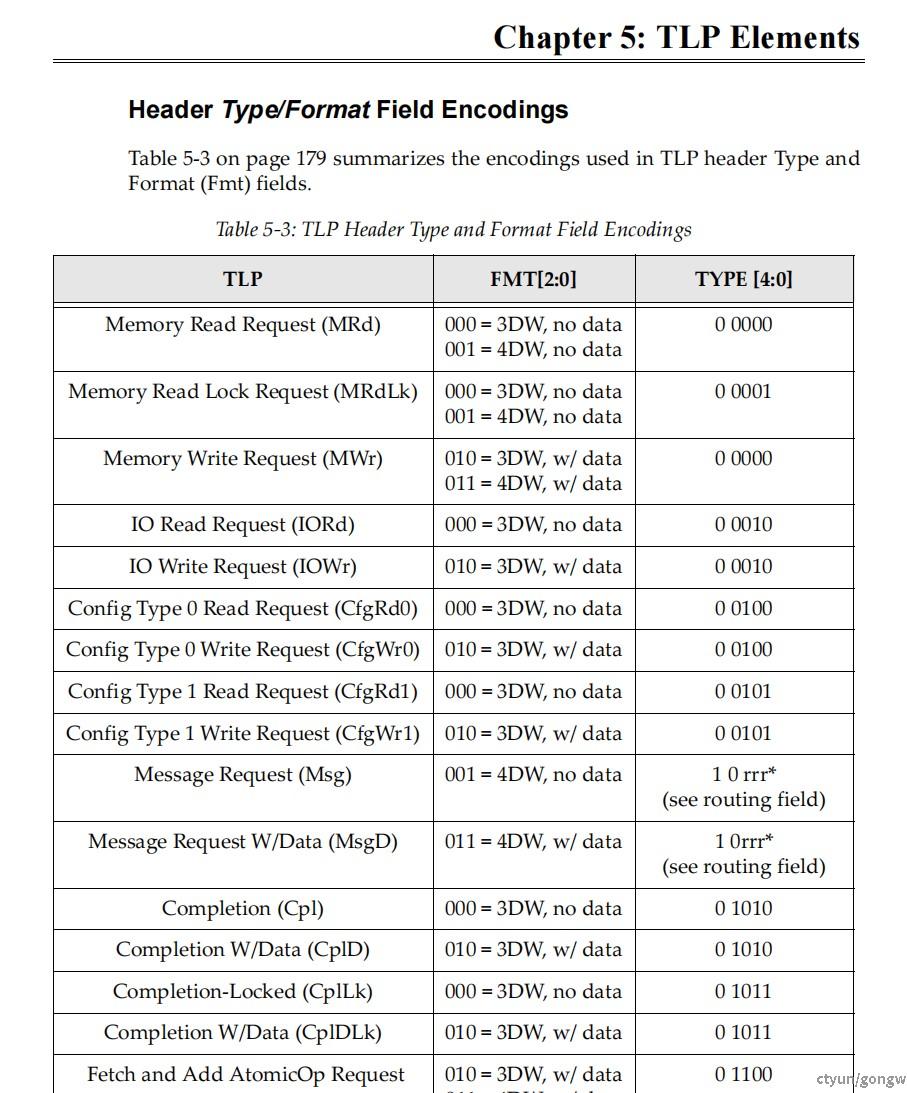

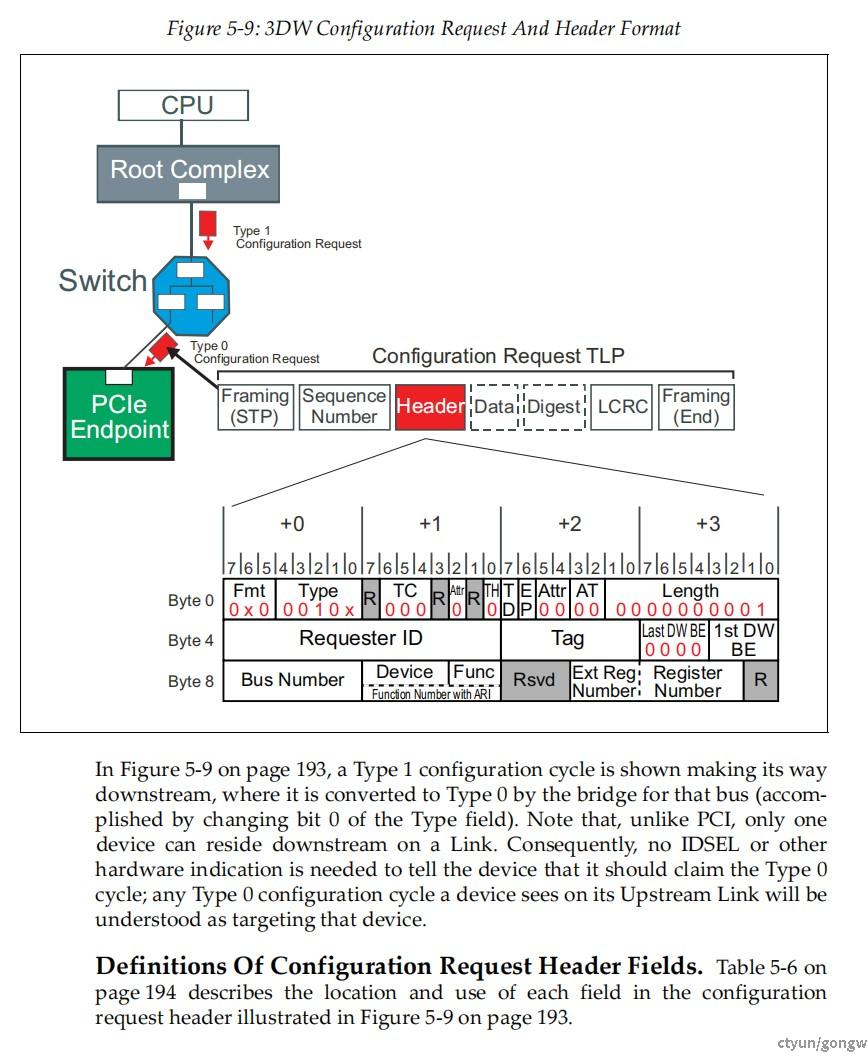

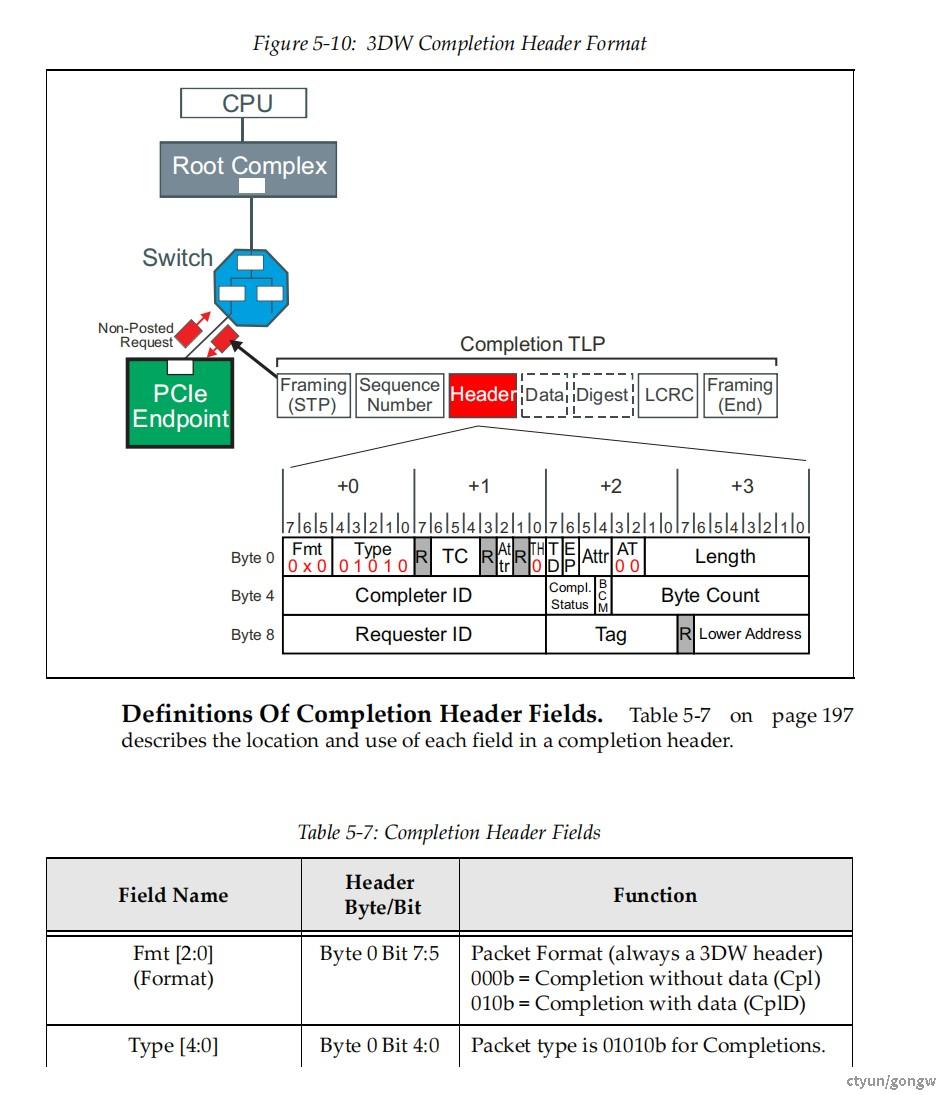

如下所示,rx均为PCIe configure Type0/1的Read Request的TLP报文,tx均为Completion/Completion W/Data的TLP报文