1.简单快捷的加固定时间,如图

此方法虽然简单便捷,但存在弊端,就是当用例开始随机,随机的流量dut处理时间很长的情况,就会存在报文没有收完就结束的情况,加长时间就会导致处理时间短的情况的用例执行时间也长了,白白浪费仿真时间和回归时间

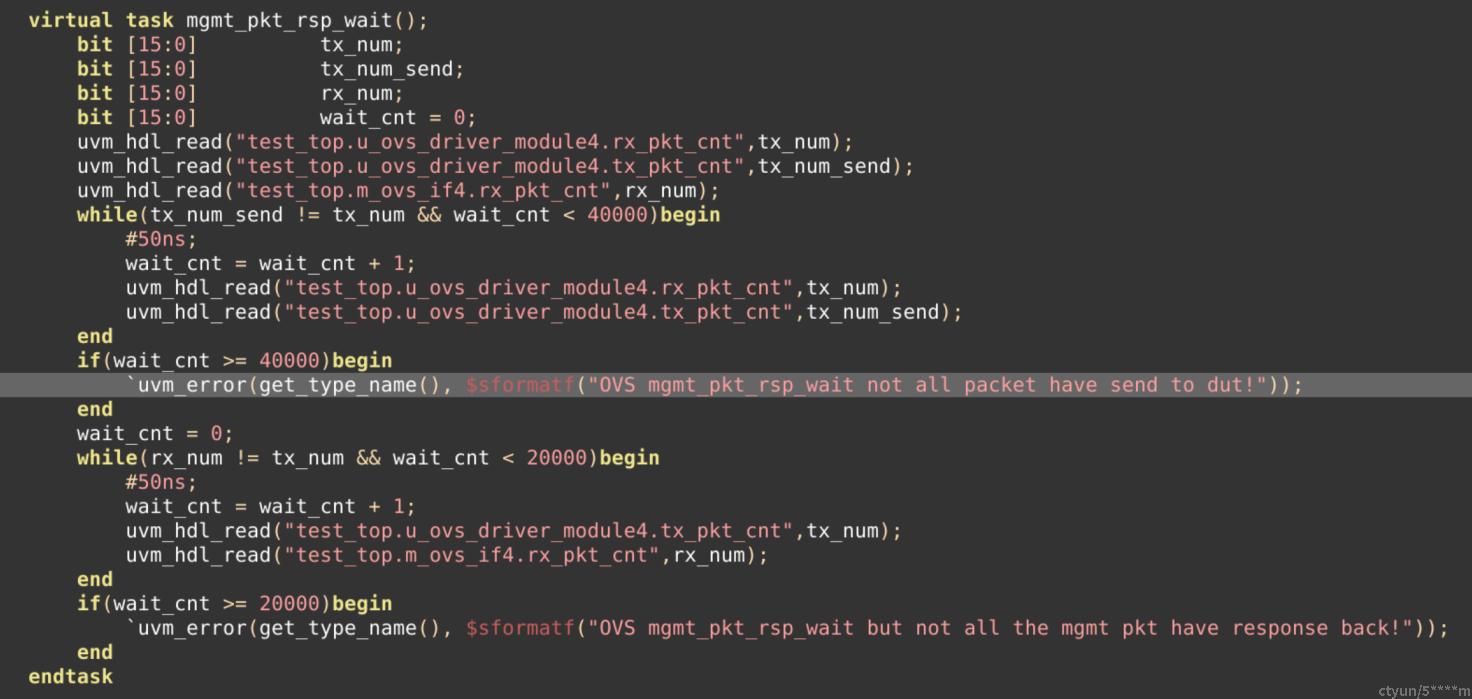

2.interface加统计,根据收取报文个数决定仿真停止时间

sequence启动后,开始监测收报个数,当收取的报文个数与发送的报文个数相等时,认为收报结束,启动drop_objection phase仿真结束;不相等则等待,当等待超时时再退出防止平台挂死。此种方法解决的无端等待的问题,同时也存在问题,当dut的处理,存在丢包的情况,不管是正常还是异常丢包,验证平台就会一直等待到超时时间到才能退出,也会影响仿真速度。

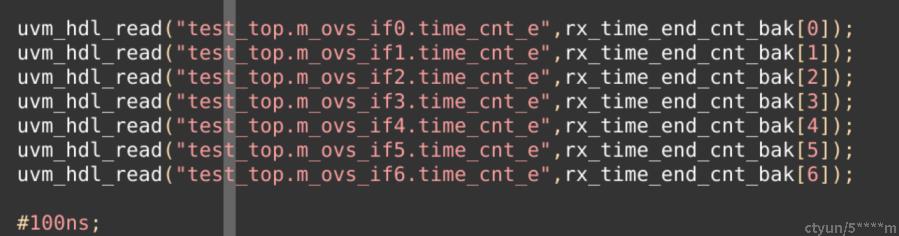

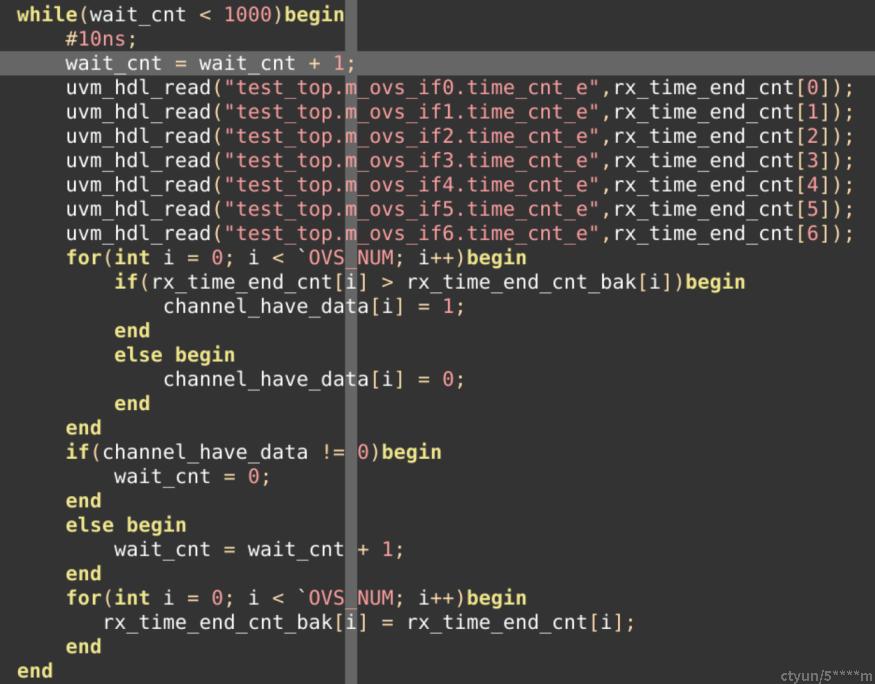

3.监测逻辑接口的出包,当没有报文转出时,仿真停止

如上截图所示,在interface上添加时间的监测,当接口上有流量的时候,刷新时间,当所有通道上的刷新时间不再变化,再启动仿真结束,完美解决上述两种方法的弊端。