UVM 验证方法学的本质

UVM(Universal Verification Methodology)是基于 SystemVerilog 的标准化验证框架,旨在构建可重用、可扩展的验证平台,覆盖从模块级到系统级的完整验证流程。其核心通过层次化组件(如 agent、env)、事务级建模(TLM)和阶段管理(phase),将验证抽象至功能层面,降低信号级调试的复杂度。但 UVM 的高度抽象也带来新挑战:事务行为与底层信号的映射关系模糊,大规模平台的错误定位效率受限,此时需要专业调试工具的支持。

verdi 的核心作用:内部信号的可视化

verdi 是常用的验证设计工具,其核心目标是解决硬件开发全流程中的调试难题(从 RTL 设计到系统级验证)。UVM+verdi的调试定位由于其具有可视化波形、信号级追踪等特点,使得问题定位及收敛的速度远大于上板调试。

verdi 的核心优势在于将硬件设计的 “抽象逻辑” 与 “具体信号” 通过可视化手段深度关联。传统的上板调试需要使用探针等工具抓取内部信号辅助问题定位,但是抓取内部信号是需要消耗硬件资源的。对于大型的逻辑电路而言,硬件资源通常十分紧张,上板调试时可以得到的内部信号有限;而且;拉取内部信号需要提前指定,灵活性不足。UVM+verdi可以模拟硬件电路的信号流,内部信号可灵活可得,从数量和灵活性上都远大于上板调试。下面以实际的问题定位介绍使用verdi进行波形定位的常用方法。

实战

仿真准备

以vcs仿真工具为例,在仿真时加入-fsdb的仿真选项生成对应的fsdb波形文件,可以使用do文件对仿真波形进行仿真层级等选项,具有很高的灵活性。

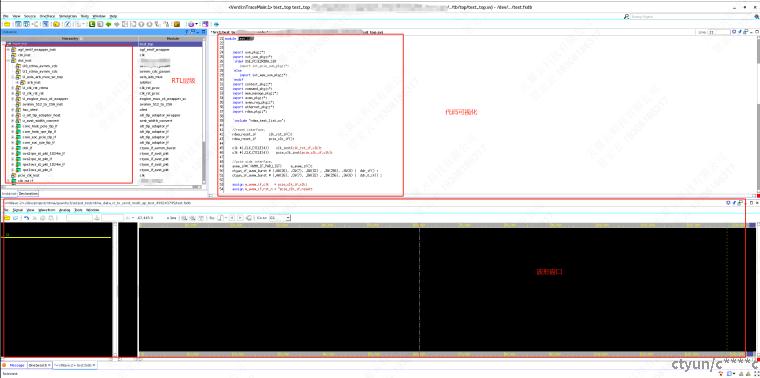

波形打开

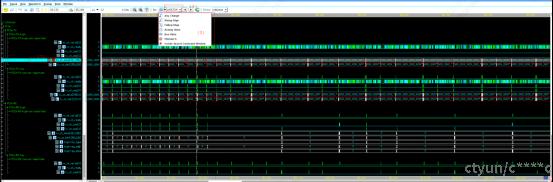

通常有两种方式打开fsdb文件。首先是可视化界面操作,在file选项中打开指定的fsdb文件;另一种方式是在启动verdi时通过-ssf选项指定波形文件。打开后的verid界面如图

信号的相关操作

显示信号值:

两种操作方式:(1)利用鼠标拖动选中信号进入波形窗口;(2)选中指定信号,使用ctrl + w,支持多选。

显示指定信号:

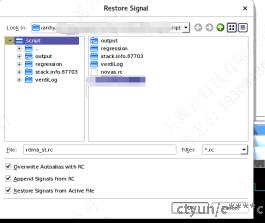

对应同一个项目,经常需要看相同的信号(例如顶层信号),无需每次打开波形都去代码中找具体的信号,打开指定rc文件快速显示信号。具体操作方式:首先显示出信号,在波形窗口shift + s,弹出save single窗口,如下图。保存到指定目录。

在波形窗口点击“r”可以打开restore singal窗口选择对应的rc文件即可。

问题定位

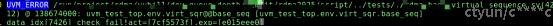

1、查看log报错。以下图数据对比报错为例,log显示pcie侧数据对比失败,实际数据为7cf5573f

2、使用波形查看硬件数据发出时间点。使用前述波形打开方法,打开波形,并显示指定信号。

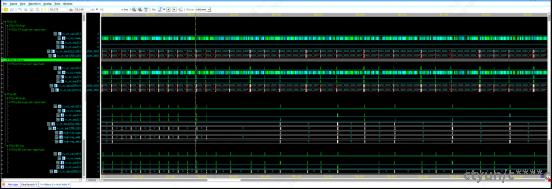

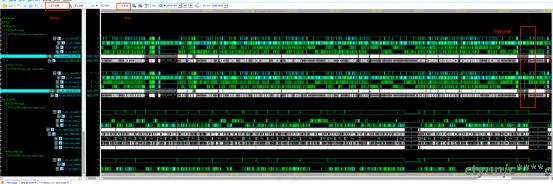

3、使用检索功能搜索数据。

(1)选择需要查找的数据,可以多选信号,本例中由于pcie的乒乓操作,需要同时检索高256位和低256位的pcie数据;

(2)选择查找选项:可以选择上升沿查找、下降沿查找、变化查找和值查找等,因为例子中出错为特定值,因此选择bus value选项;

(3)把需要查找的值填入,由于待查找的信号为256位,但是出错数据是7cf5573f,因此使用通配符“*”,检索所有包含7cf5573f的数据时间;

(4)点击左右可向前检索和向后检索;

4、确定出错时间点。虚线标志了检索结果的位置,波形视图左上角有时间点,使用ctrl+鼠标滑轮可以放大缩小波形视图,或者按住左键选择一段波形放大。

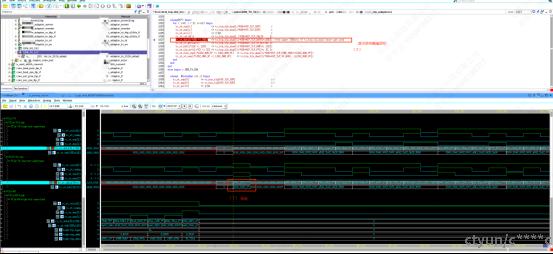

5、分析信号来源。双击波形视图中的信号,在上方的代码视图中显示该信号的来源,如图中所示,该数据来自于1027行的代码赋值。

6、追踪信号。点击赋值信号,可继续跳转到该信号的来源,同样使用ctrl + w可以得到信号的波形。重复此操作并结合代码逻辑,可以判断出是哪一模块的一段代码逻辑出错。

总结

从上述例子可以看出,使用verdi追踪波形可以追踪到内部信号,且会自动跳转到赋值逻辑,无需人工追踪赋值逻辑,不受变量名的干扰,极大的提高了问题定位的效率。