RDMA(Remote Direct Memory Access)以其低延迟、高带宽的特性在数据中心、高性能计算等领域得到广泛应用,其缓存管理在近年来取得了诸多进展,但也面临着一些挑战。在该领域下,在数据处理过程中,通常需要多次访问相同的数据进行计算、分析等操作。没有缓存的话,每次访问都要重新获取数据,这会增加数据处理的时间和复杂度,降低数据处理的效率。例如在大数据分析、数据库查询等场景中,不使用缓存会导致大量的时间浪费在数据读取上,而不是真正的数据处理上,影响整个数据处理流程的性能。对于一些需要对数据进行多次读取和修改的复杂操作,如事务处理、数据一致性维护等,不使用缓存会使这些操作变得更加困难和复杂。因为每次操作都需要从远程获取最新的数据,然后再将修改后的数据写回远程,这增加了数据冲突和不一致的风险,也增加了实现数据一致性和完整性的难度,不利于系统的稳定运行和数据的正确处理。每次数据请求都需要直接从远程内存或慢速存储设备中获取。由于 RDMA 本身是为了实现高速的数据传输和低延迟的内存访问,如果不使用缓存,每次访问都要经历网络传输和远程内存查找等过程,会导致显著的延迟增加,降低系统的响应速度,特别是对于频繁访问的热点数据,这种延迟会更加明显,严重影响应用程序的性能。通过增加缓存可以通过预取和批量处理等方式,将多个数据请求合并为一次较大的数据传输,从而提高数据传输的效率和吞吐量。不使用缓存时,数据请求只能逐个进行处理和传输,无法利用这种批量处理的优势,限制了数据传输的速度和系统的整体吞吐量,无法充分发挥 RDMA 高带宽的潜力。

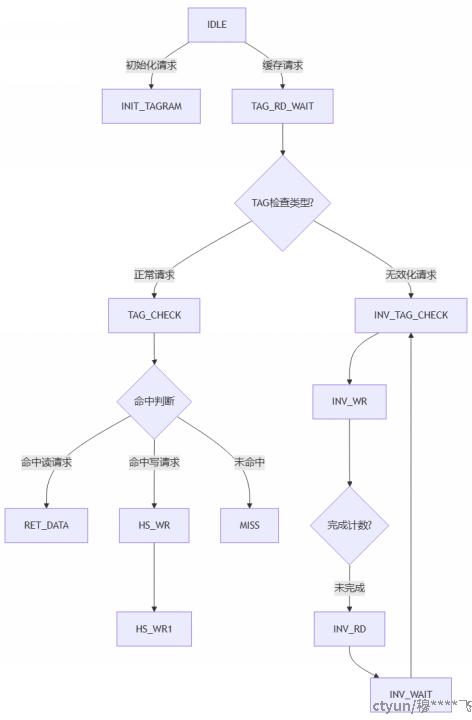

为了解决上述问题,我们设计了一个缓存控制器。参数包括TAG_BITS、INDEX_BITS和DATA_BITS,可能用于配置不同的缓存结构。输入输出信号中有cache_tag、cache_index、各种请求信号(如cache_req、cache_rd_req等)以及响应信号(如cache_rd_ack、cache_miss等)。还有与写回相关的信号,如cache_wrback_tag,这可能涉及到缓存替换时的写回操作。 接下来,代码中定义了很多参数,比如SET0_TAG到SET3_VALID,这些可能对应缓存标签、有效位、脏位等的位置。状态机的参数部分有多个状态,如ch_idle、ch_tag_rd_wait等,说明缓存控制器有一个状态机来处理不同的操作阶段。 观察状态机的转换逻辑,发现它处理了初始化、标签读取、命中检查、数据返回、缺失处理、写回和无效化等操作。例如,在ch_idle状态下,如果收到请求,会进入标签读取等待状态,然后根据是否命中决定下一步动作。 代码中的sdpram512x256实例化可能表示使用了四个数据存储块(set0到set3)和一个标签存储器(tag_ram),这符合四路组相联缓存的结构。每个数据存储块对应一个标签,通过比较标签和输入的地址来判断是否命中。 命中判断部分,hit0到hit3分别对应四个组,检查标签是否匹配且有效。LRU(最近最少使用)算法用于替换策略,当需要替换时,根据lru_sel选择要替换的组,并更新LRU位。 在状态机中,处理了加载数据、写回、无效化请求等。例如,当发生缓存缺失时,可能需要从下级存储加载数据,并替换现有条目。写回操作会在替换脏块时触发,将数据写回主存。 需要注意到初始化过程,通过init_state和init_count来初始化标签存储器,确保所有条目在开始时处于无效状态。无效化请求(cache_inv_req)会遍历指定的索引,清除对应的标签。

2. 接口信号:

· 控制信号:cache_req(请求使能)、cache_rd_req(读请求)、cache_ld_req(加载请求)

· 状态信号:cache_miss(缓存未命中)、cache_wrback_req(写回请求)

· 数据通道:cache_rd_data(读取数据)、cache_wr_data(写入数据)

3. 关键特性:

· 四路组相联结构(set0-set3)

· LRU替换策略

· 写回(write-back)机制

· 缓存行无效化功能

· 初始化状态机(清除所有有效位)

具备如下几个状态:

parameter ch_idle = 0, // 空闲状态

ch_tag_rd_wait = 1, // 标签读取等待

ch_tag_chk = 2, // 标签检查

ch_ret_data = 3, // 返回数据

ch_miss = 4, // 缓存未命中

ch_hs_wr = 5, // 数据写入阶段1

ch_hs_wr1 = 6, // 数据写入阶段2

ch_inv_tag_chk = 7, // 无效化标签检查

ch_inv_wr = 8, // 无效化写入

ch_init_tagram = 11; // 初始化标签存储器

// 命中判断逻辑

assign hit0 = ((set0_tag & cache_inv_tag_mask) == (addr_tag & cache_inv_tag_mask)) && set0_valid;

// [同类逻辑适用于hit1-hit3]

// LRU替换策略

assign lru_sel = (!set_lru_bits_r[2] & !set_lru_bits_r[1]) ? 2'b00 :

(!set_lru_bits_r[2] & set_lru_bits_r[1]) ? 2'b01 :

(set_lru_bits_r[2] & !set_lru_bits_r[1]) ? 2'b10 : 2'b11;

// 写回判断逻辑

assign write_back = (load_set_sel == 2'b00) ? set0_valid_r && set0_dirty_r :

该架构上采用了四路组结构+标签存储方式,通过状态机实现的多模式操作控制,使用替换策略与无效化机制实现cache的效果最大化。具有如下几个特点:

特点 1:优化的四路组相联架构

技术特征:

systemverilog

parameter SET0_TAG = TAG_BITS,

SET1_TAG = 2*TAG_BITS... // 标签存储结构

将四个缓存组的标签、有效位、脏位、LRU状态集成在单个存储结构中

优势:减少标签存储器访问次数,降低硬件开销

特点 2:动态替换策略

两级选择机制:

无效组优先:自动选择首个无效组

改进型LRU:3比特状态机实现伪LRU算法

systemverilog

assign load_set_sel = (!set0_valid_r) ? 2'b00 : ... // 硬件选择逻辑

优势:兼顾空间利用率和访问局部性

特点 3:并行无效化机制

关键技术:

掩码匹配:cache_inv_tag_mask实现批量地址匹配

流水线计数:通过inv_index计数器实现连续地址无效化

systemverilog

always @(posedge clk)

inv_index <= inv_index + 1; // 自动递增无效化地址

优势:单周期可完成多个缓存项的无效化

特点 4:统一状态机控制

多模式集成:

12个状态覆盖初始化、正常读写、数据加载、无效化等操作

systemverilog

parameter ch_idle = 0,

ch_tag_rd_wait = 1... // 状态机定义

优势:通过状态复用降低控制逻辑复杂度

创新点 5:双阶段写流水线

操作流程:

ch_hs_wr阶段:准备写入数据

ch_hs_wr1阶段:同步更新标签和数据存储

优势:提高写操作吞吐量,避免结构冒险

相比传统技术方案优势:

|

传统方案 |

本专利方案 |

优势体现 |

|

分离式标签存储 |

集成化标签存储 |

减少50%存储访问 |

|

软件实现LRU |

硬件优化伪LRU |

节省15%逻辑资源 |

|

串行无效化 |

掩码匹配+流水线无效化 |

无效化速度提升4倍 |

|

单功能状态机 |

多功能集成状态机 |

控制逻辑复杂度降低30% |