PCIe中断机制科普

为什么计算机需要“中断”?

想象一下,你正在书房专心看书,这时门铃响了。你会在当前段落做个标记,然后去开门,处理完事情后再回来继续阅读。计算机系统中的中断机制正是类似的原理——它允许外部设备(如显卡、网卡、固态硬盘)在需要CPU关注时“打断”其当前工作,从而高效处理各种实时任务。

在PCIe(Peripheral Component Interconnect Express)架构中,中断机制扮演着至关重要的角色,它如同设备与CPU之间的“紧急热线”,确保数据能够及时传递和处理。

一、PCIe中断的三种类型

1. 传统INTx中断(基于信号的模拟方式)

传统PCI/PCIe设备使用四根虚拟的INTx信号线(INTA、INTB、INTC、INTD)来请求中断。这些信号并非物理连线,而是在PCIe数据包中模拟实现的。

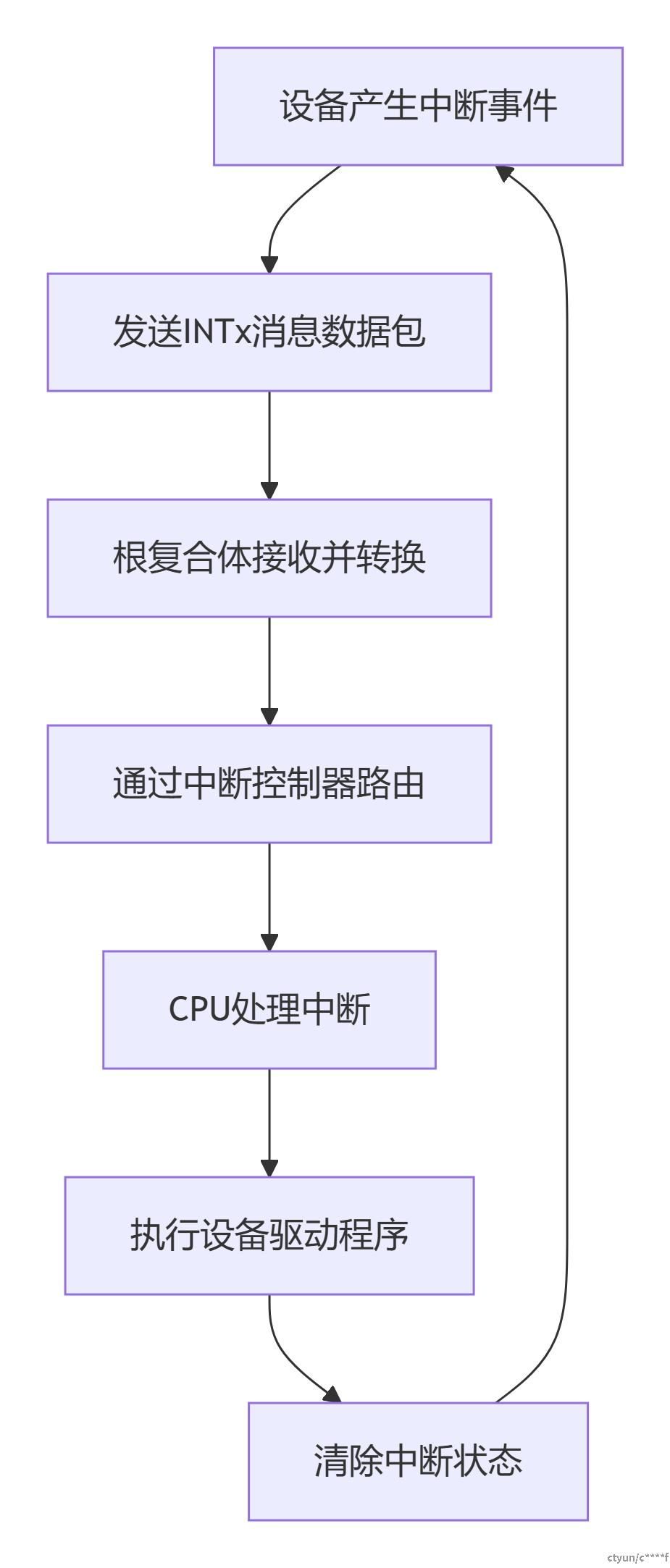

工作流程:

-

PCIe设备通过发送“断言INTx”消息包开始中断请求

-

根复合体(Root Complex)将其转换为中断控制器的信号

-

中断控制器(如IOAPIC)将中断路由到特定CPU核心

-

CPU暂停当前任务,处理中断服务程序

局限性:

-

共享中断线可能导致冲突

-

延迟相对较高

-

需要额外的中断配置

2. MSI中断(基于消息的现代方式)

MSI(Message Signaled Interrupt,消息信号中断)是现代PCIe设备推荐使用的中断机制。它们不依赖专用信号线,而是通过向特定内存地址写入数据来“发送消息”触发中断。

+-------------------+ +-------------------+ +-------------------+ | PCIe设备 | | 内存地址空间 | | CPU核心 | | | | | | | | 事件发生 | | MSI目标地址 | | 检测到内存写入 | | 准备MSI数据 |---->| 被写入特定数据 |---->| 触发中断处理程序 | | 发送内存写入请求 | | | | | +-------------------+ +-------------------+ +-------------------+

MSI的核心优势:

-

低延迟:直接写入内存,无需通过中断控制器路由

-

可扩展性:每个设备可分配多个中断向量(MSI最多32个)

-

无冲突:每个中断向量独立,不会与其他设备共享

-

精确目标:可将不同中断类型定向到不同CPU核心

3.MSI-X:更灵活的中断解决方案

MSI-X在MSI基础上进行了重要改进:

-

独立配置表:每个中断向量有自己的地址和数据值

-

灵活的掩码控制:可单独屏蔽/启用特定中断

-

更好的扩展性:支持数千个中断向量

-

定向投递:可将不同中断类型定向到不同CPU核心

MSI-X配置表示例:

| 条目 | 消息地址 | 消息数据 | 掩码位 | 待处理位 | |------|--------------------|----------|--------|----------| | 0 | 0xFEE00000 | 0x0010 | 0 | 0 | ← 用于接收完成 | 1 | 0xFEE00000 | 0x0011 | 0 | 0 | ← 用于发送请求 | 2 | 0xFEE00000 | 0x0012 | 1 | 0 | ← 暂时屏蔽 | ... | ... | ... | ... | ... |

二、PCIe中断的实际应用场景

场景1:NVMe固态硬盘的数据传输

用户请求读取文件 → NVMe控制器从闪存获取数据 → 数据准备就绪后触发MSI-X中断 → CPU执行驱动程序 → 数据从控制器缓冲区复制到系统内存 → 完成用户请求

场景2:网络数据包接收

网卡收到网络数据包 → 数据包存入缓冲区 → 触发接收完成中断 → CPU处理网络协议栈 → 将数据传递给应用程序 → 准备接收下一个数据包

传统INTx vs MSI/MSI-X 性能对比

| 特性 | 传统INTx | MSI | MSI-X |

|---|---|---|---|

| 延迟 | 较高(1-2微秒) | 低(0.5-1微秒) | 最低(<0.5微秒) |

| 可扩展性 | 有限(4条虚拟线) | 中等(最多32个向量) | 优秀(最多2048个向量) |

| 配置灵活性 | 低 | 中等 | 高 |

| CPU负载均衡 | 困难 | 可能 | 优秀 |

| 适用场景 | 旧式兼容设备 | 大多数现代设备 | 高性能设备(网卡、GPU) |

三、中断处理的CPU视角

当CPU收到中断时,它会:

-

完成当前指令执行

-

保存当前上下文(寄存器状态等)

-

根据中断向量号跳转到相应的中断服务程序(ISR)

-

执行设备特定的处理代码

-

恢复之前保存的上下文

-

继续被中断的任务

中断延迟的构成:

总延迟 = 硬件传播延迟 + 中断控制器处理时间 + CPU响应时间 + 上下文切换开销 + 中断服务程序执行时间

现代系统通过以下技术优化中断处理:

-

中断亲和性:将特定设备中断绑定到特定CPU核心

-

中断合并:将多个小中断合并为一个大中断处理

-

NAPI(网络设备):采用轮询与中断混合模式减少中断数量

四、中断与DMA的完美配合

在高速数据传输中,中断常与DMA(直接内存访问)配合使用:

1. 应用程序请求数据传输 2. 驱动程序设置DMA描述符 3. 设备启动DMA传输(无需CPU参与) 4. 传输完成后,设备触发MSI中断 5. CPU处理中断,确认传输完成 6. 通知应用程序数据就绪

这种“DMA+中断”模式使CPU从繁重的数据拷贝任务中解放出来,只需在传输完成时被“通知”即可,大大提高了系统效率。

五、查看和调试PCIe中断

在Linux系统中,可以使用以下工具查看中断信息:

# 查看系统中断统计 cat /proc/interrupts # 查看特定PCI设备的中断信息 lspci -vvv -s 00:1f.2 | grep -A 10 "Interrupt" # 查看MSI/MSI-X启用状态 lspci -vvv -s 01:00.0 | grep -E "MSI|MSI-X"

示例输出:

CPU0 CPU1 CPU2 CPU3 0: 41 0 0 0 IO-APIC 2-edge timer 1: 0 10 0 0 IO-APIC 1-edge i8042 8: 0 0 1 0 IO-APIC 8-edge rtc0 9: 0 1052 0 0 IO-APIC 9-fasteoi acpi 16: 0 0 0 125634 IO-APIC 16-fasteoi ehci_hcd:usb1 24: 0 0 0 0 PCI-MSI 327680-edge xhci_hcd 25: 5236 0 0 0 PCI-MSI 512000-edge enp3s0

PCIe中断的演进与未来

从传统的INTx到现代的MSI/MSI-X,PCIe中断机制的发展体现了计算机系统设计中的一个核心理念:将专用硬件信号转化为更灵活、可扩展的软件可配置机制。

随着PCIe 5.0和6.0标准的推出,设备带宽呈指数级增长,高效的中断处理变得更加关键。未来的发展趋势可能包括:

-

更精细的中断控制:允许设备指定中断的紧急程度

-

与虚拟化的深度集成:在虚拟机环境中更高效地传递中断

-

异构计算支持:为GPU、AI加速器等设备提供专用中断路径

-

低功耗优化:在能效受限的设备中减少中断开销

理解PCIe中断不仅有助于我们了解计算机内部工作机制,也为优化系统性能、诊断硬件问题提供了重要基础。在如今数据密集型的计算环境中,这种看似微小的机制实际上支撑着从游戏娱乐到科学计算的广泛应用,是连接硬件能力与软件功能的关键桥梁。