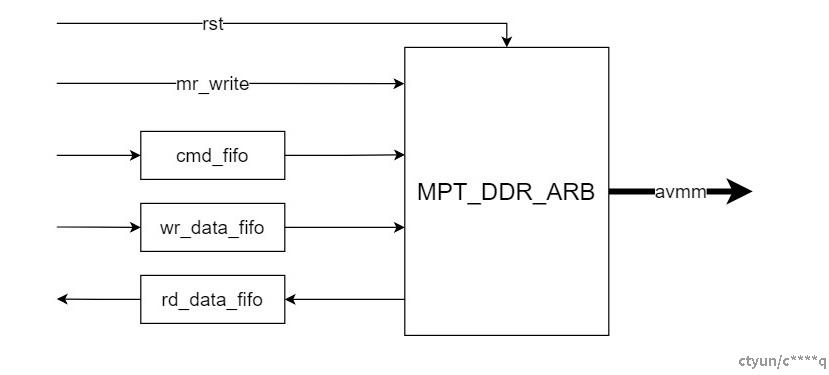

一、MPT读写接口

首先明确MPT表的读写接口,如图1所示,包含三路写接口(rst清空写、mr配置写和wr_data_fifo写)、一路读接口(rd_data_fifo读)和一路命令接口(cmd_fifo,用于传递读写标志位和读写MR_ID信息)。Csr写接口主要用于创建MR,wr_data_fifo写接口主要用于销毁MR,rd_data_fifo读接口用于读取MR,cmd_fifo命令接口用于控制读写和指定读写的MR_ID。

图1. MPT_DDR_ARB模块的读写接口

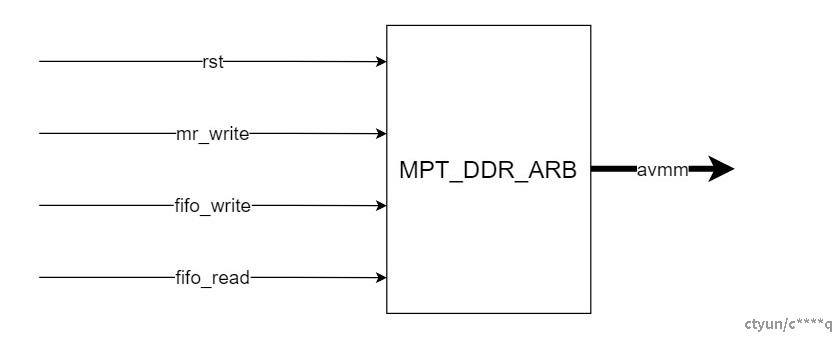

由于存在多路读写信息,因此需要使用ARB仲裁模块统一读写接口,并转化为AVMM接口向外部发送。将图1的各种接口抽象简化为读写接口如图2所示,即三路写接口和一路读接口,控制逻辑需包含在仲裁逻辑模块中。

图2. MPT_DDR_ARB接口简化抽象示意图

此外,MPT_DDR_ARB左侧的读写接口到右侧AVMM存在跨时钟域,还需要在后级增添adaptor模块用于解决跨时钟域问题。

二、FPGA中实现

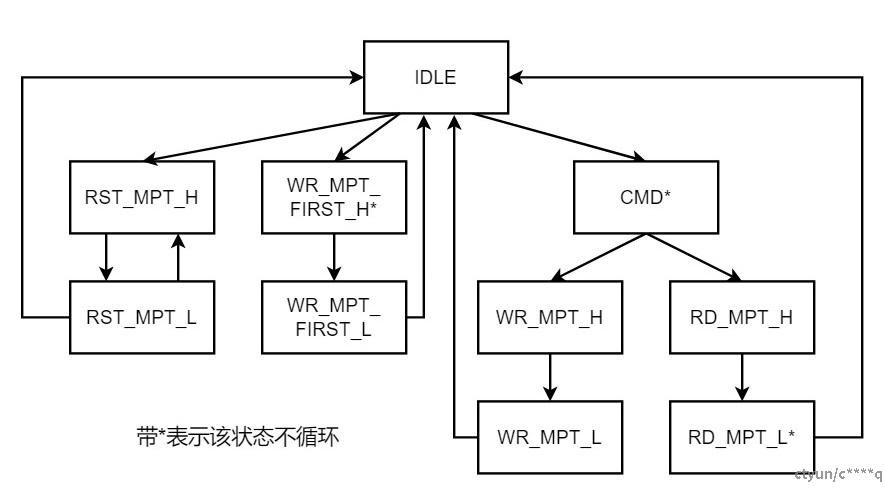

为实现以上读写信号仲裁逻辑,可以使用状态机实现,逻辑较为简单易懂,方便后期维护。状态机简化过的状态转移图如图3所示。

图3. 简化的状态转移图

状态机起始状态为IDLE,最高优先级为RST请求,其次为WR_MPT_FIRST创建MR请求,最低优先级为读取CMD_FIFO并判断读写MPT表。由于在设计中MPT_ARB左侧接口均为512bit位宽,而右侧AVMM接口为256bit位宽,因此所有操作均需按照高256bit和低256bit两个状态进行。此外,状态转移图简化了自身循环状态,仅WR_MPT_FIRST_H、CMD、RD_MPT_L状态不需要循环,其余状态均保留循环逻辑,图中不再画出。

当状态机进入RST_MPT状态时,需要将所有MPT表根据基地址全部清空,从RST_MPT_H状态开始清空高位(小端序、低地址),若检测到avmm_ready_i & avmm_write_rst则认为写入成功,跳转到RST_MPT_L状态,否则循环;在RST_MPT_L状态中同理,写入成功后跳回RST_MPT_H状态。同时,在RST_MPT_H状态时会激活计数器自增,直至自增到覆盖全部MPT表项,在RST_MPT_L状态时会检测计数器是否达到要求,若完全覆盖,则跳回IDLE状态。

当状态机进入WR_MPT_FIRST时,每次仅需写入一个MPT表项,即burst_len=2,仍然先写入高位(低地址),但由于IDLE仅当ready_i时才会跳转到WR_MPT_FIRST_H状态,因此该状态不需要循环,直接跳转到WR_MPT_FIRST_L状态,等待写入成功后跳回IDLE状态。

当状态机没有接收到RST或WR_MPT_FIRST请求,且CMD_FIFO非空时,进入CMD状态,读取CMD_FIFO,获取读写指令以及MR_ID(可映射到DDR地址),根据读写标志位进入WR_MPT或RD_MPT状态。与WR_MPT_FIRST同理,WR_MPT状态仅需写入一个MPT表项(2个AVMM地址),写操作完成后跳回IDLE。RD_MPT状态需要读取2个AVMM地址(1个MPT表项)写入到RD_FIFO中,但由于AVMM_BURST_READ的响应时间可能较长,因此这里不需要等待(状态循环),可以直接跳回IDLE,读数据逻辑不受状态机影响,只要读数据响应,就可以写回RD_FIFO中。

以上会产生三路写信号,通过MUX输出,仅RST写使用BURST_LEN=1,其余均采用BURST_LEN=2。