HPS地址映射是Intel FPGA SoC系统设计的核心概念之一,它决定了ARM处理器、FPGA逻辑以及各种外设之间如何高效地进行数据交换和控制信号传递。无论是从HPS访问FPGA资源,还是从FPGA访问HPS的存储器和外设,都需要通过精确的地址映射机制来实现。

本文将从HPS地址空间的基本结构出发,详细解析MPU视图与Non-MPU视图的差异,深入探讨HPS与FPGA之间的通信接口,并结合实际的Platform Designer设计案例,为读者提供全面而实用的HPS地址映射指导。

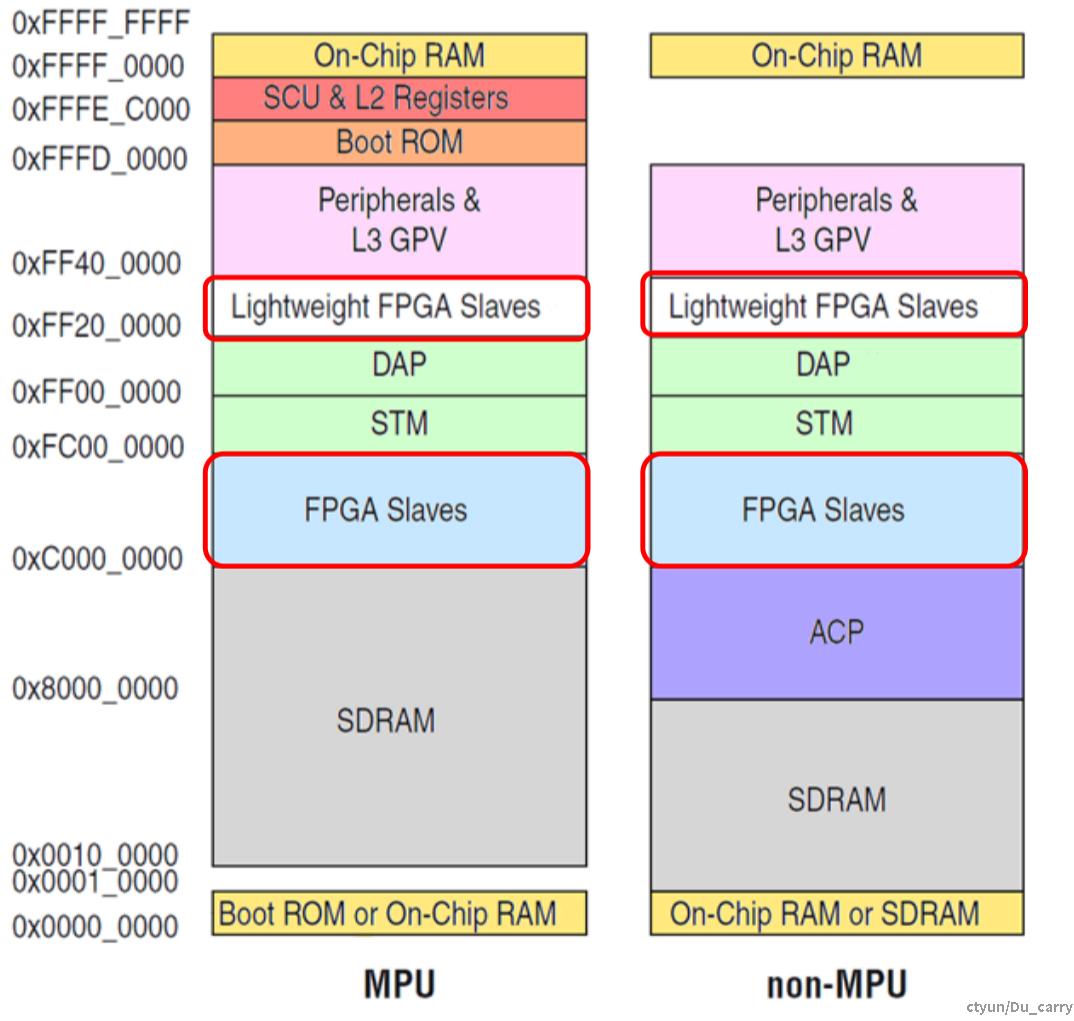

MPU与non-MPU地址空间

- HPS地址空间 左侧MPU部分是ARM处理器看到的地址空间,右侧Non-MPU是外设作为master通过L3总线访问的地址空间。要从HPS或Non-HPS访问FPGA,需要通过红框标出的FPGA Slaves和Lightweight FPGA Slaves。

- FPGA Slaves地址空间访问的是HPS2FPGA接口

- Lightweight FPGA Slaves访问的是LWHPS2FPGA接口

- MPU视图 MPU视图展示了ARM处理器如何看待地址空间:

- 要访问HPS2FPGA总线,使用FPGA Slaves定义的基地址0xC0000000作为偏移地址

- 要访问LWHPS2FPGA总线,使用Lightweight FPGA Slaves定义的基地址0xFF200000作为偏移地址

- Non-MPU视图 Non-MPU视图展示了L3总线如何看待地址空间,和MPU视图略有不同需要注意。

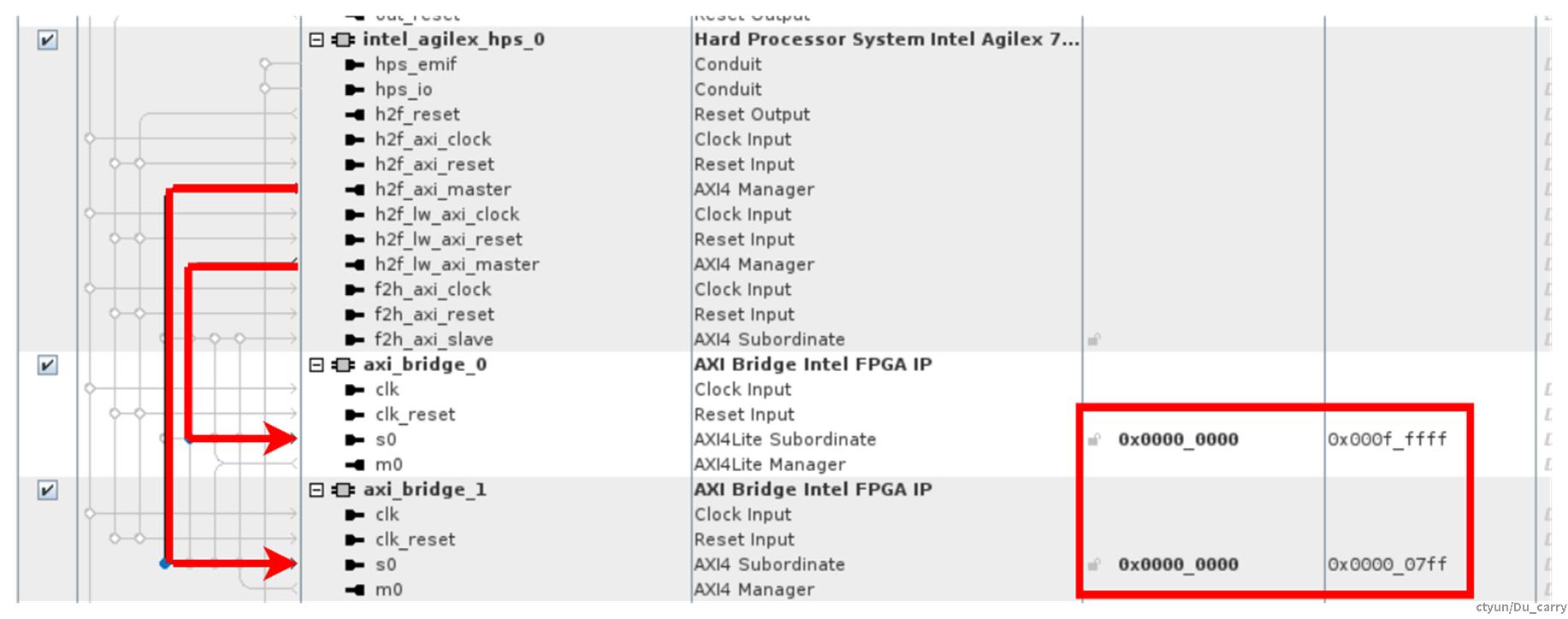

Platform Designer 地址设置

Platform Designer设计中,h2f_axi_master和h2f_lw_axi_master从Qsys看都是master接口。

- h2f_axi_master 连接到HPS2FPGA总线,图中连接到 axi_bridge_1。

- h2f_lw_axi_master 连接到 LWHPS2FPGA 总线,图中连接到 axi_bridge_0 。

- axi_bridge_1 和 axi_bridge_0 的基地址都是 0x00000000 ,这在 Qsys 中是允许的,因为每个master有各自的地址空间。Qsys中的基地址不会自动继承HPS地址空间的0xC0000000或0xFF200000,而是从0x00000000开始。

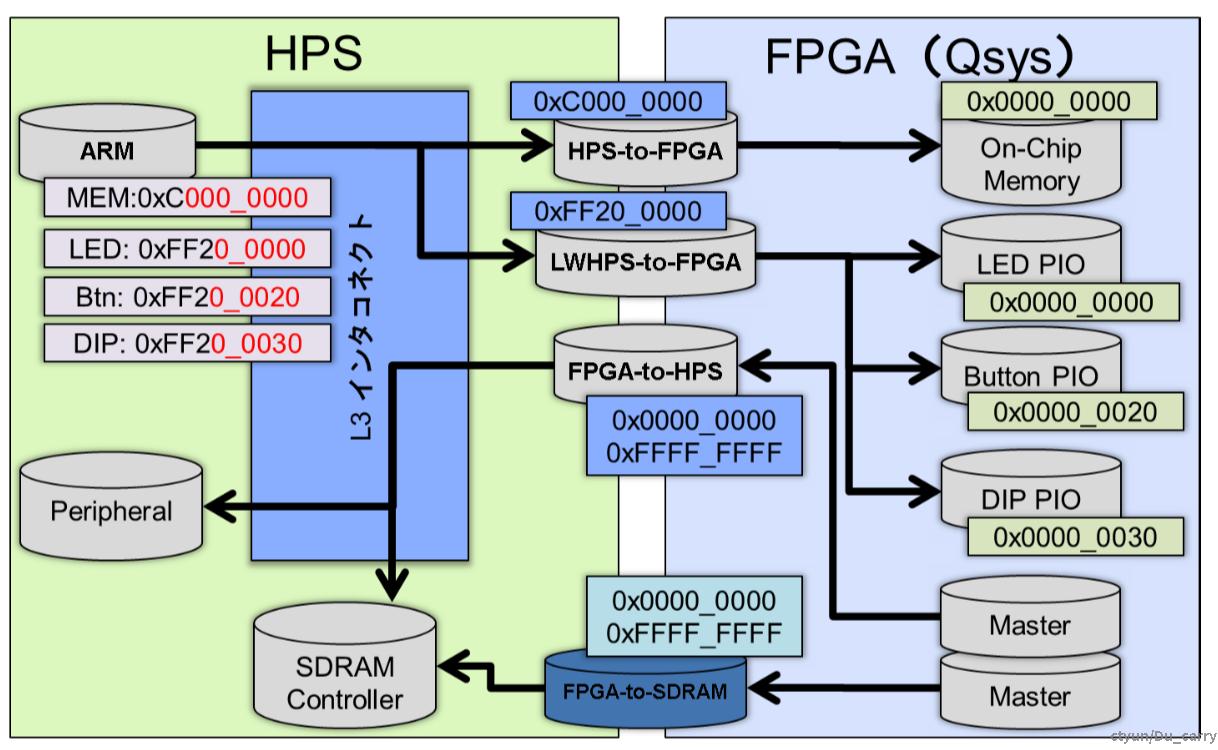

HPS与FPGA地址转换

- 从HPS看Qsys中slave的地址

要从HPS访问Qsys的slave,需要考虑HPS地址空间基地址+Qsys内偏移地址,即:- On-Chip Memory: 0xC0000000

- LED_PIO: 0xFF200000

- Button_PIO: 0xFF200020

- DIP_PIO: 0xFF200030

- 从FPGA看HPS上slave的地址

- FPGA2HPS总线接口: FPGA的master模块使用此接口访问HPS,地址范围是0x00000000~0xFFFFFFFF共4GB,遵循Non-MPU视图的地址映射。

- FPGA2SDRAM总线接口: FPGA的master模块使用此接口直接访问HPS的SDRAM控制器,地址范围也是4GB,直接对应SDRAM的地址。

上面这只是举一个例子,这个图里的地址也不是agilex芯片准确的每个master的地址,agilex的地址空间可以访问官方手册查看。

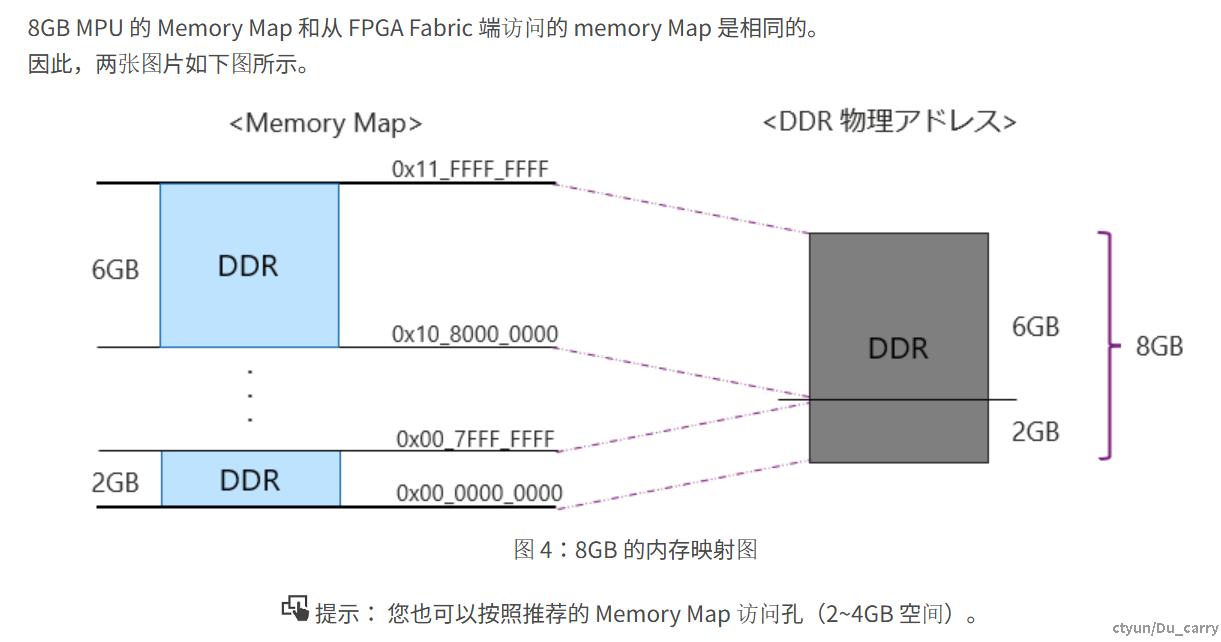

DDR相关地址映射

使用不同DDR空间大小时,DDR空间会被映射到不同的地址空间。可以查看以下查看intel官方手册来确定DDR地址空间。