1. 为什么要做“最小 HPS 系统”

在第二篇里,我们用官方 GSRD 做了一个“模板式”上手:

- 硬件工程几乎已经配置好;

- 软件(U‑Boot + Linux + RootFS)也有预编译镜像;

- 适合快速验证开发板功能。

但在实际项目中,经常会遇到这些情况:

- 使用的是自研板卡,而不是官方开发板;

- DDR 拓扑、位宽、速率与官方板子不同;

- 需要裁剪掉大量不需要的外设和逻辑,只保留最核心的 HPS + 少量外设;

- 希望掌控从硬件到软件的每一个配置细节,而不是“黑盒”式使用 GSRD。

这时就需要一套不依赖 GSRD 的通用方法,来构建一个“最小 HPS 系统”:

- 只例化 HPS IP + HPS 外部内存接口(EMIF);

- 让 HPS 能够正常初始化 DDR、跑起来 FSBL / U‑Boot / Linux;

- 后续再按需往 FPGA 侧挂自定义 IP。

本文就专注于这条“最小硬件主干”的搭建,软件与启动流程放到第四篇详细展开。

2. 最小 HPS 硬件系统长什么样?

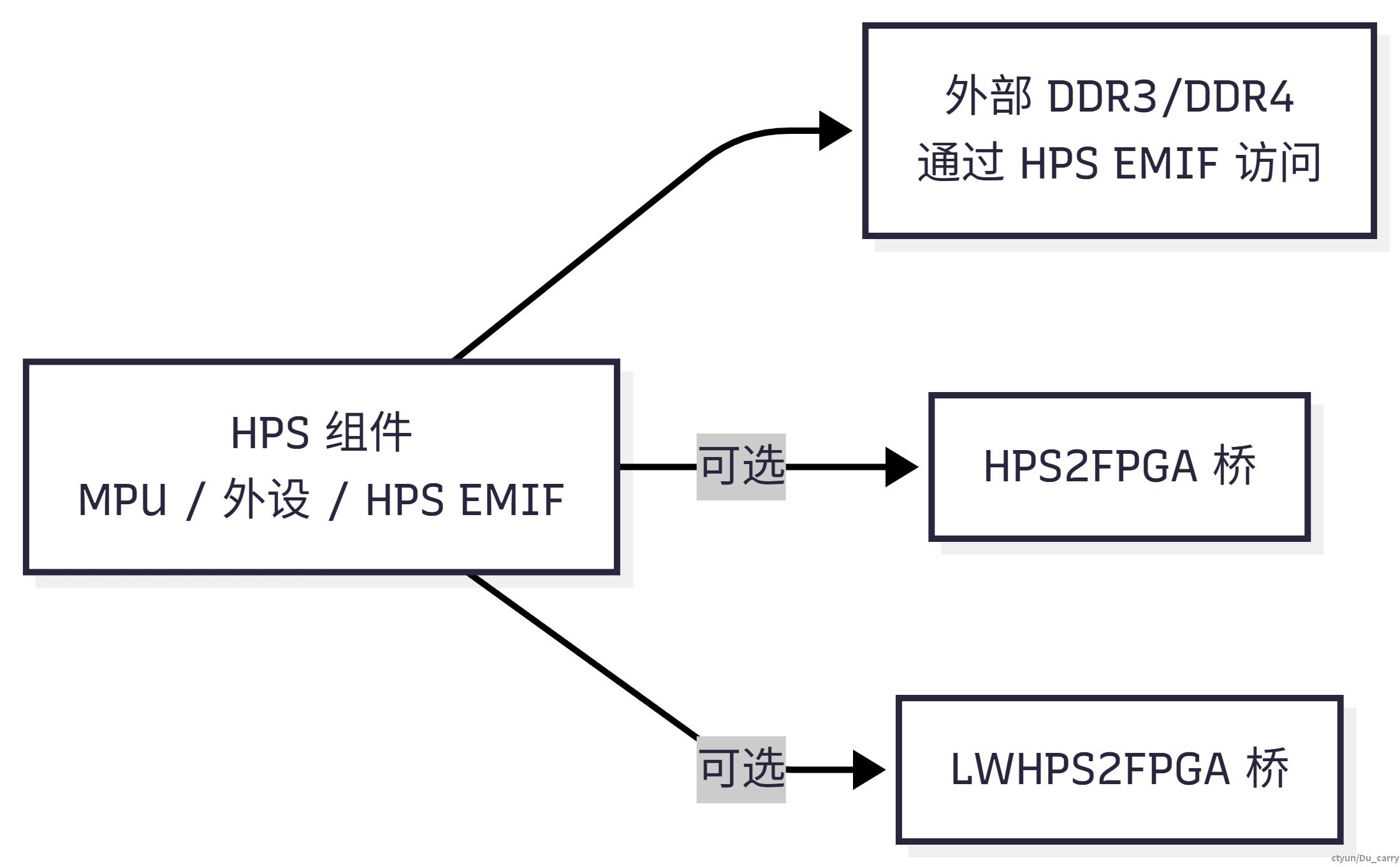

从 Platform Designer(Qsys)的视角看,一个最小可用的 HPS 系统可以抽象成下面这张图:

关键点只有两条:

- **HPS 必须能访问外部存储器(DDR)**这是 HPS 跑 FSBL/U‑Boot/Linux 的基础。对 Agilex / Cyclone V / Arria 10 SoC 来说,这通常由 HPS 组件内部的 EMIF 子模块 完成,或者通过专用的 HPS EMIF 端口接到外部 DDR。

- FPGA 逻辑可以先不要,桥接接口可以先不开

为了把问题收敛到“让 HPS 正常启动”这一件事上,我们可以暂时不连接任何自定义 FPGA 逻辑,只把 HPS + 外部 DDR 这条路径打通。

如果确定后续会用到 HPS→FPGA 的访问,可以提前把HPS2FPGA/LWHPS2FPGA桥打开,但不用挂复杂 IP。

换句话说,一个“最小 HPS 系统”在硬件上只需要:

- HPS IP(含 MPU、外设、时钟/复位和 HPS EMIF);

- 与 HPS EMIF 连接的 DDR3/DDR4 芯片;

- 必要的时钟与复位电路;

- 少量启动相关外设(如 SD/eMMC、QSPI、UART)对应的 HPS 专用引脚。

其它外设和 FPGA 逻辑,都可以留到后续演进中再接入。

3. 在 Quartus + Platform Designer 中从零创建最小 HPS 系统

下面以 Agilex 7 SoC 为例,给出一个从空工程开始的“最小 HPS 系统”搭建流程。对于 Cyclone V / Arria 10 SoC,步骤类似,只是界面和 IP 名称略有差异。

3.1 新建 Quartus 工程并选择 SoC 器件

- 打开 Quartus Prime(推荐 Pro 版,对 Agilex 支持更完整)。

- 新建工程,选择对应的 SoC 器件(例如某个 Agilex 7 SoC 型号)。

- 暂时不添加任何顶层 RTL 文件,只保留一个空的顶层(后面由 Platform Designer 生成系统并实例化)。

如果有板卡厂商提供的 .qsf / .sdc / board preset 文件,建议一开始就导入,以减少后面手动约束的工作量。

3.2 在 Platform Designer 中例化 HPS 组件

- 在 Quartus 中打开 Platform Designer(Qsys)。

- 在 IP Catalog 中找到类似

HPS或SoC HPS的组件,双击添加到系统中。 - 如果板卡厂商提供了 HPS 相关的 board preset / XML 描述:

- 在 HPS IP 的参数配置界面选择对应板卡预设;

- 这样可以自动带出 HPS EMIF、外设引脚分配、时钟等默认设置。

如果没有现成预设,则需要根据芯片手册和板卡原理图手动配置:

- 选择 HPS 外设启用情况(UART、SPI、I2C、SDMMC、EMAC 等);

- 选择 HPS EMIF 通道的类型、位宽、Bank 绑定等(详见第 4 节)。

此时本质上你已经拥有了一个“自带 DDR 控制器的 HPS 模块”,只不过还没有把引脚接出来。

3.3 处理 HPS EMIF 与 DDR 的连接

如果 HPS 组件内部已经集成 EMIF(典型的 Agilex / Arria 10 SoC 场景):

- 在 HPS 参数中启用 HPS EMIF;

- 选择外部 DDR 类型(如 DDR4)、数据位宽(如 32 位)、Bank 位置等;

- Platform Designer 会自动生成一组 HPS EMIF 相关的引脚(DQ/DQS/ADDR/CLK 等),在系统生成后导出到顶层。

如果是需要单独例化 EMIF IP 的架构(部分老器件):

- 在 Platform Designer 中再添加一个

External Memory Interface (EMIF)IP; - 选择内存类型(DDR3/DDR4 等)、数据位宽、频率等;

- 将 EMIF 的控制/数据接口连接到 HPS 的 EMIF 端口;

- 将 EMIF 的物理引脚(DQ/DQS/ADDR/CLK 等)导出为顶层端口。

无论哪种方式,核心目标不变:HPS 必须通过某个 EMIF 通道访问到板上的 DDR 芯片。

3.4 配置 HPS 时钟与复位

在 HPS IP 的参数界面中,一般会有类似 Clocks and Resets 的选项卡,这里要做几件事情:

- 选择 HPS 的外部输入时钟源:

- 例如板卡上的 25 MHz/100 MHz 晶振,通过某个 HPS 专用引脚输入;

- 频率要与板级原理图一致。

- 确认 HPS EMIF 相关的 PLL 和时钟分频设置:

- 内部会根据 DDR 速率自动给出推荐值,但可以结合 EMIF 用户手册微调;

- 需要满足 DDR 芯片数据手册的时序要求。

- 配置 HPS 复位脚:

- 一般需要一个外部全局复位输入,与板卡的电源时序、按键复位电路配合;

- 同时确认内部各子模块(MPU、外设、EMIF)的复位关系。

建议在这一阶段就把板卡原理图摊开,对照 HPS 的 clocks & resets 界面逐项核对,避免后期反复改动。

3.5 预留 HPS↔FPGA 桥接接口(可选)

虽然“最小 HPS 系统”在理论上只需要 HPS + DDR,但从工程演进角度看,通常会预留以下接口:

HPS2FPGA:高带宽 AXI 接口,后续可用于大数据通路;LWHPS2FPGA:轻量级接口,适合访问寄存器类 FPGA IP;- 可选的

FPGA2HPS/FPGA2SDRAM接口,用于 FPGA 作为主机访问 HPS 或 DDR。

在 HPS IP 中启用这些桥接后,Platform Designer 会自动导出对应的 master/slave 端口(如 h2f_axi_master、h2f_lw_axi_master)。

在“最小系统”阶段,可以先不连接任何 FPGA 侧 IP,只是保持这些接口处于启用状态,后续再挂 PIO、DMA 或自定义逻辑。

3.6 导出顶层端口并生成系统

完成 HPS IP 配置后,在 Platform Designer 中:

- 对需要连接到板卡的信号(主要是 HPS EMIF 和 HPS 外设专用引脚),勾选

Export导出为系统端口; - 运行系统生成,生成 HDL 封装(Verilog/VHDL)和

.qip工程文件; - 回到 Quartus 顶层设计中:

- 实例化刚刚生成的 Platform Designer 系统;

- 把系统导出的端口,连接到顶层端口(对应实际器件的引脚)。

随后在 .qsf 中为这些顶层端口分配管脚(可以参考板卡厂商提供的 pin 限制文件),在 .sdc 中添加必要的时钟/时序约束。

3.7 完整编译并检查 HPS/EMIF 报告

最后,执行一次完整编译(Analysis & Synthesis + Fitter + Timing):

- 在 Fitter 报告中检查:

- HPS EMIF 是否成功放置和布线;

- DDR 引脚是否被正确分配到支持 EMIF 的 I/O Bank;

- 是否有

no legal placement或 I/O 标准冲突等错误。

- 在 TimeQuest 报告中检查:

- DDR 相关时钟域的时序是否满足收敛要求;

- 是否存在明显的 hold/setup 问题。

如果器件支持 EMIF 校准(calibration),后续在板上上电时也需要通过硬件测试确认 DDR 校准通过,这一点将在第四篇结合启动流程一起说明。

4. HPS EMIF / DDR 配置中的几个关键参数

在实际配置 HPS EMIF 时,容易踩坑的几个参数可以单独拎出来说一下。

4.1 数据位宽(HPS EMIF DQ Width)

HPS EMIF DQ Width 决定了 HPS 访问 DDR 时的数据总线宽度,例如:

- 16 位、32 位,甚至更宽;

- 位宽越大,理论带宽越高,但对板级布线、Bank 资源占用的要求也更高。

这个参数必须与板卡的实际连线匹配,一般按下面的顺序确定:

- 查板卡原理图:确认 DDR 芯片与 SoC 之间的数据线数量(DQ 数);

- 查芯片手册和 EMIF 用户指南:确认该 SoC 上对应 Bank 支持的最大/推荐位宽;

- 在 HPS EMIF 或 EMIF IP 参数中设置对应的

DQ Width,并选择合适的 DQS 组和 Bank。

如果设置与板卡不符,轻则导致 DDR 校准失败,重则直接无法正常启动系统。

4.2 内存类型与速率

在 EMIF 配置中,一般至少需要设置:

- 内存类型:DDR3 / DDR3L / DDR4 / LPDDR4 等;

- 工作电压 / I/O 标准(通常由板卡硬件固定);

- 数据速率:如 800 MT/s、1600 MT/s 等。

建议做法:

- 优先使用器件或板卡厂商提供的 preset,它会带出一组经过验证的参数;

- 如果确有需要修改(例如自定义板卡),则严格对照:

- DDR 芯片数据手册中的 AC / DC 时序要求;

- Intel EMIF 用户指南中的参数说明和推荐值。

4.3 地址映射与 Bank 交错

对于跑 Linux 的 HPS 系统来说,DDR 通常被视为一块连续的物理地址空间。但在 EMIF 内部,可以通过地址映射和 Bank 交错来优化性能:

- 行/列/Bank 位分配方式;

- 是否启用 Bank 交错(interleaving);

- 是否启用 ECC 等。

在“最小 HPS 系统”的第一版中,完全可以先沿用 preset 的默认设置,只要:

- 物理容量与实际芯片匹配;

- HPS 侧看到的 DDR 地址区间满足启动链路(FSBL/U‑Boot/Linux)的需求。

更复杂的映射和性能优化,可以在系统稳定后再逐步调整。

5. 最小 HPS 系统中的地址空间认知

虽然本篇主要讲硬件,但在 HPS 系统里,“能不能正确访问 DDR / 外设寄存器”最终都体现在地址映射上。

在一个典型的 Intel SoC FPGA 中,HPS 的 MPU 视角下大致会看到:

- 一段连续的 DDR 地址空间(通过 HPS EMIF 访问外部 DDR);

- 一段 片上 SRAM / OCRAM;

- 若干 HPS 外设寄存器区域(UART、SPI、I2C、EMAC 等);

- 若干 桥接窗口(HPS2FPGA、LWHPS2FPGA 等)映射到 FPGA 侧。

在“最小系统”阶段,我们至少要确认两件事:

- DDR 的物理地址区间与 FSBL / U‑Boot / Linux 配置一致;

- 如果启用了 HPS→FPGA 桥接,将来要访问 FPGA 寄存器时,要搞清楚:

- HPS 侧的桥接基址(例如

0xFF200000一类的地址); - Platform Designer 内部每个从设备的偏移地址;

- 最终访问地址 = 桥接基址 + Qsys 偏移。

- HPS 侧的桥接基址(例如

关于完整的 HPS 地址映射和 L3 互连重映射寄存器,可以在后续深入主题中展开,最小系统阶段只要确认“DDR 区域正确可用”即可。

6. 小结

本篇从硬件工程的角度,把“最小 HPS 系统”的核心要素拆解成几步:

- 只例化 HPS + EMIF,先把 HPS→DDR 这条主干打通;

- 在 Platform Designer 中配置 HPS EMIF、时钟、复位以及可选的 HPS↔FPGA 桥接;

- 导出顶层端口,分配管脚和时序约束,完成一次完整编译并检查 EMIF 报告;

- 在这一过程中重点关注 DDR 类型、位宽、速率和地址映射等关键参数。

这样我们就得到了一套不依赖 GSRD、只依赖芯片和板卡硬件本身的最小 HPS 硬件系统。